Mi SciELO

Servicios Personalizados

Articulo

Indicadores

-

Citado por SciELO

Citado por SciELO

Links relacionados

-

Similares en

SciELO

Similares en

SciELO

Compartir

Ingeniería Electrónica, Automática y Comunicaciones

versión On-line ISSN 1815-5928

EAC vol.38 no.2 La Habana may.-ago. 2017

ARTÍCULO ORIGINAL

Variantes de sistema de almacenamiento para un detector de radar en el espacio de los momentos

Storage System Variants for a Radar Detector in the Moments Space

Camilo Guillén Soriano I, Carlos Luis Marcos Rojas II, Nelson Chávez Ferry I

I Departamento de Telecomunicaciones y Telemática de la Facultad de Telecomunicaciones y Electrónica de la Universidad Tecnológica de La Habana "José Antonio Echeverría", CUJAE. La Habana, Cuba.

II Centro de Estudios Biomédicos (CEBIO) de la Facultad de Automática y Biomédica de la Universidad Tecnológica de La Habana "José Antonio Echeverría", CUJAE. La Habana, Cuba.

RESUMEN

Los detectores de radar con toma de la decisión en el espacio de los momentos (método DRACEC), requieren muestrear los parámetros de las señales provenientes de la región explorada y almacenar estas muestras teniendo en cuenta la célula resolutiva que les dio origen. El presente artículo propone la implementación en FPGA de dos variantes de sistema de almacenamiento, cada una de la cuales garantiza la identificación precisa de la célula que corresponde a un determinado conjunto de muestras. La primera variante está basada en sistemas digitales secuenciales que controlan una memoria RAM estática, mientras que la segunda utiliza un microprocesador en conjunto con memorias RAM internas al FPGA. Los sistemas desarrollados permiten el almacenamiento ordenado de las muestras como se requiere para las etapas posteriores de los detectores de radar que empleen el método DRACEC.

Palabras claves: FPGA, memorias RAM, método DRACEC.

ABSTRACT

Radar detectors with decision making in the moments space (DRACEC method), require sampling the signals parameters from the scanned region and storing these samples taking into account the resolution cell that originated them. The present article proposes an FPGA implementation of two variants for the storage system, each one of this guarantees precise identification of the cell that corresponds to a certain set of samples. The first variant is based on sequential digital system that control a static RAM, while the second uses a microprocessor in conjunction with internal RAM in the FPGA. The developed systems allow orderly samples storage as required for later stages of radar detectors using the DRACEC method.

Key words: FPGA, RAM memory, DRACEC method.

1. INTRODUCCIÓN

El método DRACEC [1], acrónimo de Detección de blancos de Radar por Análisis y Clasificación Estadística de la emisión Celular, permite alcanzar elevadas probabilidades de detección en ambientes de baja relación señal a ruido. Además, es un método paramétrico y adaptativo, aplicable a escenarios donde las distribuciones estadísticas de las variables aleatorias que intervienen en la toma de la decisión sean desconocidas o difíciles de estimar. DRACEC está basado en un procesamiento estadístico que emplea muestras de gran tamaño de parámetros como la amplitud, fase, polarización, etc. de las señales dispersadas por las células resolutivas que componen la región de búsqueda. Como característica fundamental de este procesamiento se obtiene un vector de clasificación (patrón), cuyas componentes (rasgos) son algunos de los momentos de tales parámetros, posibilitando la clasificación de las células resolutivas en una de dos clases: fondo (blanco ausente) o anomalía (blanco presente). Debido a que las variables aleatorias utilizadas en DRACEC para el proceso de decisión son un conjunto finito de momentos, normalmente se hace referencia al sistema que lo emplee como un detector en el espacio de los momentos, distinguiéndose así de las técnicas tradicionales.

El procesamiento de las eco-señales provenientes de las células en que ha sido dividida la región de búsqueda, realizado por el método DRACEC, consta de tres etapas fundamentales [1]: Adquisición, Adaptación al fondo y Detección de anomalías. Normalmente, la señal de video del receptor se aplica a la etapa de adquisición, ver Figura 1, conjuntamente con el pulso de disparo para el sincronismo y la referencia angular. En esta etapa, la señal de video continua se digitaliza para formar las muestras aleatorias del tamaño requerido, una por cada célula, las cuales son almacenadas mediante un sistema que constituye el centro de este trabajo, siendo renovadas al final de cada período de exploración. Por su parte, en la etapa de adaptación al fondo se calculan los momentos estadísticos de las muestras y partiendo del criterio de mantener un nivel constante de probabilidad de falsa alarma, el espacio de decisión queda dividido en dos regiones, a una de ellas corresponde la clase fondo, mientras que a la otra corresponde la clase anomalía. Finalmente, los resultados de la adaptación son utilizados por la etapa de detección para asignar cada célula como perteneciente al fondo o a la anomalía.

Es común tomar a la amplitud como parámetro de la señal sometido a análisis [2, 3] y en lo adelante este será el caso abordado, de manera que la aplicación de DRACEC requiere el almacenamiento de sus muestras para el posterior cálculo de los momentos. Surge entonces la necesidad de diseñar un sistema de almacenamiento que satisfaga las exigencias impuestas por el método en cuanto a capacidad y ordenamiento adecuado de las muestras, ya que en dependencia de la célula resolutiva que les dio origen, el sistema deberá permitir la identificación unívoca de los patrones -calculados a partir de estas muestras- en la etapa de decisión.

En este trabajo se propone una solución a la problemática anterior, dividida en dos variantes de diseño: la primera está basada en lógica secuencial y una memoria SSRAM (siglas en inglés de Memoria de Acceso Aleatorio Sincrónica y Estática), mientras que la segunda utiliza un microprocesador en conjunto con memorias RAM sintetizadas internamente en el FPGA. Como será abordado, comprobar que los sistemas propuestos garantizan el almacenamiento ordenado de las muestras constituye el principal objetivo de este trabajo. Además, cada una de estas variantes presenta sus propias ventajas en dependencia de la aplicación concreta, por lo que otro de los objetivos consiste en mostrar las características de ambas en cuanto a capacidad de almacenamiento, frecuencia máxima de trabajo y consumo de elementos lógicos del FPGA.

La implementación de los sistemas de almacenamiento se realizó en un kit de desarrollo para el Procesamiento Digital de Señales [4] que cuenta, entre otros elementos, con un FPGA Cyclone II del fabricante Altera, 2 conversores analógico a digital (A/D) modelo AD5500 de 14 bit y 125 MSPS (siglas en inglés de Millones de Muestras por Segundo), 2 conversores digital a analógico (D/A) modelo DAC904 de 14 bit y 165 MSPS, y un chip SSRAM modelo Cypress CY7C1360C. A continuación, se describen los sistemas correspondientes a las dos variantes, mientras que posteriormente se aborda el funcionamiento de estos y su utilidad para el almacenamiento ordenado de las muestras como se requiere en los detectores DRACEC.

2. VARIANTE 1: LÓGICA SECUENCIAL PARA ATENCIÓN A LA SSRAM

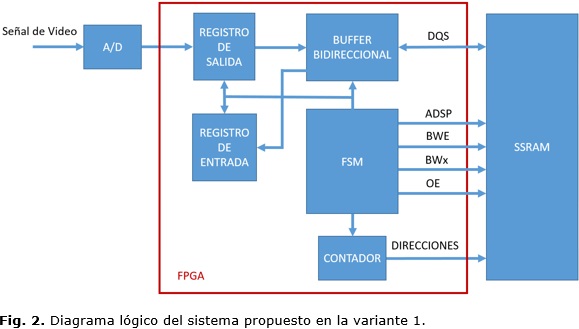

La primera variante para el sistema de almacenamiento, mostrada en la Figura 2, está compuesta por una memoria SSRAM externa al FPGA del kit de desarrollo disponible, controlada mediante lógica secuencial diseñada por los autores y un conversor A/D. La SSRAM cuenta con una capacidad de 256Kx36 bits o sea 262144 locaciones de 36 bits [5], accedidas a través del bus de direcciones de 18 bits (DIRECCIONES en la figura), un bus bidireccional para entrada/salida (DQS) de las muestras y 4 señales de control (ADSP, BWE, BWx y OE).

Con el objetivo de proporcionar los comandos de control a la memoria, se diseñó una máquina de estados finita (FSM por sus siglas en inglés) responsable del funcionamiento del sistema con el sincronismo requerido. En el caso del bus de datos DQS, debido a que este es tanto de salida como de entrada, se utiliza un búfer bidireccional para recibir y enviar las muestras desde y hacia la memoria según se requiera. Además, por la naturaleza inestable de este tipo de búfer [6] es necesario almacenar el dato leído o el que está a punto de escribirse, mediante los registros de entrada y salida, respectivamente. Como se observa en la Figura 2, el direccionamiento de la memoria se realiza a través de un contador, controlado por la máquina de estados, que permite la paginación en el almacenamiento de las muestras, lo cual implica que la memoria se divida en sectores (páginas) correspondientes a las células resolutivas de la zona explorada. Lo anterior posibilita la identificación precisa de la célula que originó un conjunto de muestras determinado, de manera que cuando se requiera realizar el cálculo de los momentos correspondientes a dicha célula, sean extraídas de la memoria las muestras correctas, tal como se comprobará más adelante.

4. VARIANTE 2: MICROPROCESADOR NIOS II PARA CONTROLAR MEMORIA RAM INTERNA

En esta alternativa se utilizan las facilidades que brinda Altera para implementar en un solo componente, funciones que se realizan por separado en la variante anterior, como son: la atención a los buses de datos, control, dirección y la lógica principal que controla toda la operación. En este sentido el constructor SOPC (siglas en inglés de Sistema sobre Chip Programable) constituye una poderosa herramienta de desarrollo incluida en el Quartus II. Utilizándolo es posible definir y generar un sistema completo en un tiempo menor, ya que SOPC automatiza la tarea de interconectar los componentes de hardware prediseñados [7]. Altera y otros desarrolladores proveen varios componentes en el constructor SOPC, entre los que sobresalen: microprocesadores, como el Nios II, controladores de DMA y temporizadores, interfaces para comunicaciones serie como UART (siglas en inglés de Transmisor y Receptor Asincrónico Universal) y SPI (siglas en inglés Interfaz Serie de Periféricos), puertos de entrada y salida de propósito general e interfaces para dispositivos externos [8, 9].

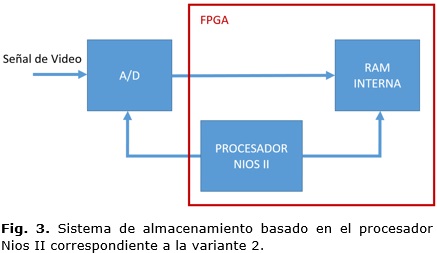

El núcleo de los sistemas diseñados mediante SOPC lo constituye el procesador Nios II, el cual está definido en lenguaje de descripción de hardware. Además, puede ser implementado en tres configuraciones diferentes: una versión rápida diseñada para alto rendimiento, una versión estándar y una versión económica, la cual se utiliza en el presente trabajo debido a que requiere la menor cantidad de recursos del FPGA, aunque es también la más limitada en cuanto a las propiedades configurables por el usuario. Como se muestra en la Figura 3, el Nios II en conjunto con un arreglo de memorias RAM internas con capacidad para 140000 bytes, resultan los componentes esenciales de la segunda variante para almacenar las muestras como requiere el detector DRACEC.

4. VERIFICACIÓN DEL FUNCIONAMIENTO DE LOS SISTEMAS PROPUESTOS

La región de exploración en un sistema de radar que emplee el método DRACEC puede estar compuesta por cientos de células resolutivas. No obstante, y con el objetivo de comprobar el funcionamiento correcto de los sistemas diseñados, se propone un acercamiento a una situación real de operación, simulando el proceso de adquisición para una región de búsqueda con cinco células resolutivas, resaltando que esto se realiza sólo para verificar que el almacenamiento con paginación se efectúa correctamente. El hecho de simular solamente cinco sectores de memoria no constituye una limitante para el sistema propuesto, ya que los cambios a realizar para su implementación en una región con mayor cantidad de células resolutivas serían prácticamente insignificantes, siendo suficiente cambiar una constante en el código VHDL que describe al contador en la primera variante, mientras que en la segunda las modificaciones se realizarían en el programa del microprocesador.

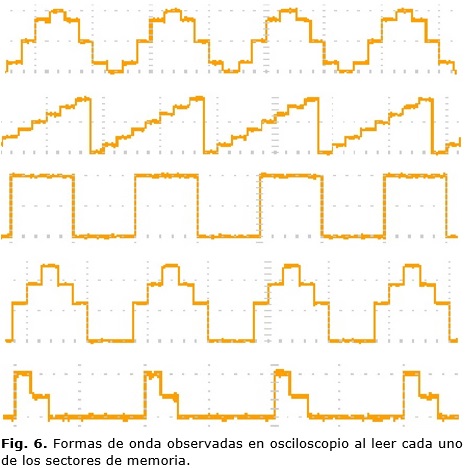

El objetivo del experimento consiste en almacenar cinco señales periódicas con formas de onda diferentes (equivalentes a las muestras provenientes de cinco células resolutivas), en sus sectores de memoria correspondientes, tal como se ilustra en la Figura 4. Las muestras se intercalan en distintos intervalos de tiempo, cada uno de los cuales resulta proporcional a la distancia de la célula que le dio origen, permitiendo simular la señal de la etapa de video en el receptor (V(t) en la Figura 4). El funcionamiento correcto de los sistemas de almacenamiento para ambas variantes, requerirá que cuando sea adquirida la primera muestra de la primera señal, se ordene la escritura con la dirección de la primera locación del primer sector de memoria, posteriormente se cambiará la dirección hacia la primera locación del segundo sector (donde se almacena la primera muestra de la segunda señal) y así sucesivamente hasta que se escriba la primera muestra de la quinta y última señal, lo que provoca que el sistema retorne al primer sector de memoria pero esta vez apuntando a su segunda locación, ciclo que sería repetido hasta adquirir la cantidad de muestras deseada.

Los valores de amplitud a almacenar se generaron mediante la herramienta Matlab, obteniendo cinco señales periódicas de ocho muestras, cuyas formas de onda aproximadas se observan dentro de los sectores de memoria representados gráficamente en la Figura 4. Con el objetivo de utilizar estas señales en el entorno de Quartus II, las ocho muestras de cada una de ellas se convirtieron a binario como enteros con signo de 14 bits y se almacenaron en cinco memorias ROM (siglas en inglés de Memoria de Sólo Lectura) de ocho localidades. Posteriormente, mediante varios contadores y un multiplexor, las señales fueron intercaladas en tiempo a razón de una muestra cada 50 ns, permitiendo simular la señal de video en una situación real de operación, ya que cada muestra corresponde al eco proveniente de la célula con el retardo específico que esta provoca. Así, por ejemplo, las muestras que estén separadas 250 ns, corresponderán a la misma célula resolutiva y por tanto se almacenarán en el mismo sector de memoria (ver Figura 4). En la Figura 5 se observa mediante osciloscopio la señal de video simulada.

Para las dos variantes propuestas, la señal de la Figura 5 se introdujo a los sistemas de almacenamiento encargados de acomodar las muestras en los sectores correspondientes. Al finalizar el almacenamiento, se procedió a leer el contenido de cada uno de los sectores obteniendo, como era de esperar, las señales mostradas en la Figura 6. En ambas variantes los resultados fueron idénticos y satisfactorios, observándose el cumplimiento de los objetivos propuestos al almacenar de forma ordenada en sectores de memoria diferentes, las muestras de cada una de las cinco formas de onda. Las señales de las Figuras 5 y 6 fueron tomadas mediante un osciloscopio conectado a uno de los conversores D/A del kit utilizado.

En la Tabla 1 se observan las características de ambas variantes en cuanto a la cantidad de muestras por cada una de las células resolutivas que sería posible adquirir en cada caso, la frecuencia máxima de trabajo y el consumo de elementos lógicos del FPGA. Para estos resultados se tomaron muestras de 14 bits debido a que esa es la resolución del conversor A/D empleado. La variante 1 supera a la 2 en todos los aspectos analizados: presenta mayor capacidad de almacenamiento, mayor frecuencia de trabajo y menor consumo de recursos del FPGA. No obstante, el diseño y la implementación mediante la variante 2 resultan más sencillos, debido a las posibilidades ofrecidas por la herramienta SOPC para utilizar componentes prediseñados que aceleran el desarrollo de sistemas complejos.

5. CONCLUSIONES

Los resultados obtenidos y su correspondencia con los deseados demuestran que los sistemas diseñados, en cada una de las dos variantes propuestas, posibilitan el almacenamiento ordenado de las muestras de amplitud en diferentes sectores de memoria, tal como requieren los detectores DRACEC. La variante 1 utiliza lógica secuencial conjuntamente con SSRAM externa al FPGA, proporcionando un mayor control sobre el diseño, mayor capacidad de almacenamiento, mayor frecuencia máxima de trabajo y menor consumo de recursos en comparación con la variante 2, basada en el procesador Nios II. Sin embargo, esta última requiere menor complejidad para su desarrollo ya que emplea componentes predefinidos que facilitan la implementación. En ambas alternativas se logró recrear una situación similar a la operación real de un sistema de radar, ya que cada una de las señales generadas puede interpretarse como la respuesta electromagnética de las células que componen la región explorada, las cuales serán sometidas a análisis mediante la aplicación del método DRACEC para determinar la presencia o no de un blanco en cada una de ellas.

REFERENCIAS

1. Chávez N. Detección y Alcance de Radar: La Alerta Temprana de Blancos en Fondos Enmascarantes y una Solución al Problema. [Tesis presentada en opción al grado científico de Doctor en Ciencias]. La Habana: Instituto Técnico Militar "José Martí"; 2002. Disponible en http://www.biblioteca.cujae.edu.cu

2. Chávez N, Bacallao J, Guillén C. Análisis de la Calidad de la Detección de Blancos de Radar por el Método DRACEC. In: XVII Scientific Convention of Engineering and Architecture; La Habana (Cuba); 2014.

4. Altera Corporation. Cyclone II DSP Development Board Reference Manual 2006.

5. Cypress Corporation. Introduction to Cypress SRAMs - AN1116. 2006.

7. Altera Corporation. Quartus II Handbook Version 9.0 Volume 4: SOPC Builder 2009.

8. Altera Corporation. Introduction to the Altera SOPC Builder Using VHDL Designs. 2010.

9. Altera Corporation. Introduction to the Altera Nios II Soft Processor. 2010.

Recibido: 23 de diciembre del 2016

Aprobado: 24 de febrero del 2017

Camilo Guillén Soriano, Recibió el título de Ingeniero en Telecomunicaciones y Electrónica del Instituto Superior Politécnico "José Antonio Echeverría", CUJAE, en el 2013. Desde ese mismo año labora en el Departamento de Telecomunicaciones y Telemática de la Facultad de Telecomunicaciones y Electrónica de la Universidad Tecnológica de La Habana "José Antonio Echeverría", CUJAE. Correo electrónico: camilo.gs@tele.cujae.edu.cu.