Introducción

Un sistema de antenas con formación digital del haz es un arreglo de antenas donde la información adquirida por cada una se digitaliza y envía a un bloque de procesamiento para conformar la respuesta espacial del conjunto [1]. Su empleo ofrece ventajas con respecto a los sistemas analógicos por lo que su desarrollo ha tomado fuerza en la actualidad. Patrick K. Bailleul, en su trabajo [2], expone las ventajas del formador digital del diagrama direccional y valora su empleo en aplicaciones de comunicación satelital.

Un desarrollo de gran utilidad es presentado por Sheila Luisa en [3]. El trabajo muestra el diseño de un convertidor digital de bajada como parte de un sistema de antenas inteligentes. La implementación se efectúa sobre un FPGA, pero está limitada a aquellas desarrolladas por Xilinx. Además, solo incluye una de las etapas necesarias para el desarrollo de los sistemas con formación digital del diagrama de radiación. A pesar de las limitantes brinda una solución escalable que permite su desarrollo futuro.

Los estudios realizados por Yogesh [4] y Liang [5] exponen la implementación de formadores de haces durante la transmisión de señales. El primero emplea la síntesis digital directa para obtener las señales correspondientes a cada canal. Un FPGA realiza los controles necesarios para la generación en función de la dirección de radiación deseada. El segundo también garantiza el procesamiento digital con un FPGA, pero en este caso se emplea para ajustar los coeficientes de peso aplicados a cada canal.

Otros proyectos centran su análisis en los algoritmos adaptativos desarrollados para procesar el conjunto de señales recibidas. En este grupo se encuentra el documento [6] de Xiaodong Wang, el cual muestra la implementación del algoritmo LCMV (del inglés Linearly Constrained Minimum Variance[7, 739-751]) sobre un FPGA. Para su desarrollo se utiliza las herramientas de síntesis del Entorno de Desarrollo Integrado Vivado; en [8] se muestra información detallada sobre estas. En el trabajo de Iftikhar Rasheed [9] se materializa una de las ventajas del empleo de sistemas con formación digital del diagrama de radiación: la integración de algoritmos de estimación espectral y formadores de diagramas. En este caso son combinados el LMS (del inglés Least Mean Square) y el MUSIC (Acrónimo de Multiple Signal Classification).

En Cuba existen antecedentes del desarrollo de antenas con formación digital del diagrama. Trabajos como el de Sheila Luisa [3], Rolando Guerra [10] y Ramírez [11] constituyen referencias del tema. En [10] se muestra un desarrollo de antenas inteligentes para RFID (del inglés, Radio Frequency Identification) sobre FPGA de la familia Xilinx con el empleo del Matlab and System Generator para el diseño del sistema. Por otra parte, [11] expone la implementación del procesador para un sistema con formación convencional del diagrama de radiación sobre un FPGA de la familia Altera.

Aunque se trata de un tema con amplia divulgación científica, en el estudio realizado se pudo apreciar que el desarrollo de arreglos de antenas con formación digital del diagrama direccional está sujeto a dificultades y desafíos tecnológicos. A pesar de su importancia y significación estos no son tratados directamente en la mayor parte de la bibliografía disponible. Se destacan cuestiones asociadas al factor de forma de los elementos del sistema, consumo y costo de los componentes del diseño, exigencias de selectividad y linealidad de los receptores en función de las características del diagrama direccional que se desea realizar digitalmente, igualdad en las respuestas de frecuencias de los canales de procesamiento, alineamiento temporal, operación coherente en radiofrecuencia y exigencias al procesador de los datos.

Peter Delos en su trabajo [12] propone el empleo de transceptores de radiofrecuencia integrados para garantizar las etapas previas a la formación digital del diagrama direccional. Esto facilita el flujo del diseño total del sistema y los tiempos de implementación. Sobre esta base se desarrollan plataformas especializadas como la mostrada en [13] formada por cuatro transceptores AD9081 para un total de 16 canales. El acceso a dichas tecnologías es limitado, sin embargo, es posible emplear tarjetas más simples para obtener desarrollos similares. Los problemas en este caso radican en la configuración y control de las tarjetas, garantizar el sincronismo y la coherencia de los múltiples canales de recepción y lograr la calibración de las señales de cada antena. Seguidamente es posible pasar a la formación del diagrama direccional. Al realizarse de forma digital se pueden formar tantos diagramas como sean necesarios y lo permita la plataforma de procesamiento utilizada [2].

El objetivo de este trabajo es diseñar e implementar un sistema con múltiples diagramas direccionales simultáneos formados digitalmente en banda S a partir de las señales recibidas por un arreglo de cuatro antenas. Para la recepción de las señales se utiliza la tarjeta de evaluación ARRadio formada por el integrado de radiofrecuencia AD9361. Como elemento de control y procesamiento se propone el FPGA de la familia Stratix IV ubicado en la tarjeta de desarrollo TR4. Se propone un procedimiento basado en la Transformada de Fourier para la calibración de cada canal de recepción.

Las contribuciones fundamentales de este trabajo son: la configuración y control del transceptor integrado AD9361 mediante el empleo de FPGA, el diseño en Simulink del bloque de procesamiento para la formación digital de la característica direccional y su implementación en un FPGA. Además, se expone un procedimiento basado en la Transformada de Fourier para la calibración de cada canal de recepción de acuerdo a los trabajos realizados por Guolong He [14] e Ilgın [15].

Materiales y métodos

Esta sección incluye temas relacionados con la teoría de formación del diagrama de radiación en arreglos de antenas, el desarrollo de sistemas digitales con el empleo del FPGA, la utilización del Matlab para la creación de códigos HDL sintetizables y el uso de tarjetas transceptoras para la recepción de señales de radio.

Formación del diagrama de radiación convencional en arreglos de antenas

Sobre un sistema formado por N antenas ubicadas aleatoriamente en el espacio incide un frente de onda plano procedente de la dirección espacial caracterizada por los ángulos ( s y ( s . En la Figura 1 se representa la situación expuesta con anterioridad. Los puntos A n con coordenadas (px n , py n , pz n ) indican la ubicación de cada antena; el subíndice n varía desde 1 hasta N e identifica el elemento bajo análisis.

La diferencia entre las señales recibidas por los elementos del arreglo está determinada por la variación del retardo que sufre la onda para llegar a cada una de las antenas y depende de la ubicación de estas con respecto al centro de referencia del sistema de coordenadas, la dirección de incidencia de la onda y su frecuencia.

Las antenas realizan un muestreo espacial del frente de onda incidente. Para reconstruir la señal de entrada se debe introducir en cada canal un coeficiente de peso w n que compense la diferencia de recorrido de la onda y a continuación efectuar la suma vectorial de las señales resultantes. El valor de los coeficientes está determinado por la expresión (1) [16] donde λ representa la longitud de onda de la señal. El resto de los términos que intervienen en la ecuación fueron definidos anteriormente y están asociados a la dirección de arribo de la señal y la ubicación de las antenas.

El diseño propuesto en el presente trabajo se centra en un arreglo lineal donde los elementos se encuentran dispuestos a lo largo del eje z. En este caso se anulan las componentes de posición px n y py n , por lo que la expresión (1) queda simplificada como se muestra en la ecuación (2).

Los coeficientes de peso aplicados al arreglo de antenas definen la forma en que el sistema filtra espacialmente las señales en su entrada. La representación gráfica de la característica de filtrado se denomina diagrama direccional e indica la intensidad relativa de campo con la cual ocurre la recepción de señales desde las diferentes direcciones [17]. La medición práctica del diagrama de radiación permite validar la correcta determinación y aplicación de los coeficientes de peso.

Los elementos expuestos anteriormente constituyen la base del funcionamiento de los sistemas con formación convencional del diagrama direccional. En estos se recibe con su máxima intensidad las señales procedentes de la dirección angular empleada para el cálculo de los coeficientes de pesos y se atenúan el resto de las señales correspondencia con el diagrama direccional.

La formación del diagrama direccional puede ser realizada de forma analógica o digital. En la primera la aplicación de los pesos y suma de los canales es garantizada con el empleo de lentes o matrices de alimentación, sumadores o distribuidores de potencia en radiofrecuencia. Adicionalmente pueden incluir desfasadores y atenuadores o amplificadores controlados para cada canal. La señal resultante es entregada a uno o varios receptores según el tipo de formador de diagrama direccional. En los sistemas con formación digital del diagrama (DBF, del inglés Digital Beamforming) la información procedente de cada antena se procesa digitalmente. El primer paso necesario es la calibración de los canales digitales para garantizar la coherencia total entre estos. Tras la calibración se efectúa la formación del diagrama direccional. Mediante la aplicación de los pesos adecuados puede obtenerse cualquier forma del diagrama direccional de la antena.

Un sistema DBF está compuesto por cuatro secciones fundamentales: arreglo de antenas, bloque de radio frecuencia, receptor digital y procesador para la formación del diagrama direccional. Este trabajo se concentra en el desarrollo de los últimos componentes: el bloque de radio frecuencia y el receptor digital integrados en cada AD9361 y el procesador desarrollado en el FPGA para la formación de múltiples canales digitales.

Tarjetas transceptoras para la recepción de señales de radio

El desarrollo alcanzado en los circuitos integrados de alta frecuencia ha permitido la fabricación de microcircuitos transceptores con alto grado de integración y capaces de efectuar todas las tareas realizadas por un transmisor y un receptor de radio. Un ejemplo típico es el transceptor de radiofrecuencia AD9361. Este integrado opera en la banda de frecuencias de 70 - 6000 MHz con ancho de banda instantáneo de hasta 56 MHz. Desde el punto de vista de adquisición de señales, incluye dos canales independientes de recepción directa con control automático de ganancia (90 dB de rango de regulación), filtrado digital y corrección de errores de cuadratura y offset [18].

También se han desarrollado tarjetas formadas por dichos componentes para facilitar su configuración, control y empleo. La tarjeta de evaluación ARRadio optimizada para 2400 MHz incluye en su composición al integrado AD9361 y un conector de alta velocidad (HSMC, del inglés High Speed Mezzanine Card) con el objetivo de acoplar las señales necesarias para la manipulación del transceptor.

Existen trabajos que sustentan el empleo de integrados de radiofrecuencia para la fabricación de arreglos de antenas con formación digital del diagrama de radiación. Entre estos es posible citar la plataforma de 16 canales transceptores expuesta en [13] donde se utilizan cuatro transceptores AD9081. De igual forma, Hussain Naqvi en su trabajo [19] muestra la utilización de circuitos integrados de radiofrecuencia como una de las tendencias actuales en el desarrollo de arreglos de antenas.

Procesador digital sobre fpga

El procesador para la formación digital de los múltiples diagramas en el sistema de antenas expuesto puede ser realizado en diversos dispositivos programables. Los procesadores digitales de señales (DSP, por sus siglas en inglés) y FPGA son los más utilizados. El estudio realizado mostró una tendencia al empleo de los últimos como núcleo de procesamiento. En el trabajo de Sener Dikmese [20] se compara un algoritmo implementado en un representante de ambos dispositivos en cuanto a exactitud, tiempo de procesamiento y utilización relativa de recursos. Como resultado se mostró una ligera ventaja en la utilización de FPGA lo cual coincide con la línea de diseño actual.

En el presente trabajo se escogió la tarjeta de desarrollo Terasic TR4 con el objetivo de utilizar sus conectores HSMC para conectar las tarjetas transceptoras necesarias para la adquisición de cuatro canales de radiofrecuencia. La configuración, control y formación digital del diagrama direccional se realiza en el FPGA Stratix IV presente en el TR4.

Parte del proceso de la descripción del hardware del sistema se realiza sobre la plataforma de simulación multidominio Simulink perteneciente al Matlab. Esta posee un conjunto de librerías con posibilidad de exportación a VHDL sintetizable [21] accesibles desde la ventana de comandos mediante la sentencia hdllib. Con esta herramienta se facilita el flujo del diseño y su verificación. El esquema sintetizado tiene la ventaja de poder ser empleado en cualquier familia de dispositivos FPGA.

Implementación del sistema con múltiples diagramas direccionales simultáneos

En esta sección se explica la estructura general del sistema y se aborda su funcionamiento. También se detallan los bloques y esquemas desarrollados para garantizar el proceso de recepción, calibración y la formación digital de los múltiples diagramas direccionales simultáneos.

Esquema general del sistema

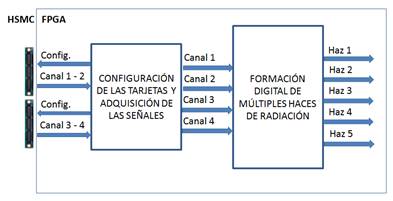

El esquema general puede ser analizado en dos secciones: etapa de radiofrecuencia y bloques de procesamiento digital. La primera incluye la recepción y digitalización de las señales recibidas por cada antena. La segunda el procesamiento necesario para la formación digital de múltiples diagramas direccionales simultáneos. En la Figura 2 se representa la composición de la etapa de radiofrecuencia y su núcleo fundamental compuesto por las tarjetas transceptoras ARRadio.

Cada uno de los ARRadio tienen a su entrada las señales procedentes de dos antenas, en su interior realizan la recepción directa y su digitalización. Estas señales son enviadas a través de dos conectores HSMC presentes en la tarjeta de desarrollo Terasic TR4 hacia el interior de la FPGA Stratix IV. Los conectores HSMC funcionan además como puentes para el envío hacia el AD9361 de las señales para su configuración con el empleo de líneas de comunicación serie SPI (del inglés Serial Peripherical Interface). En esta etapa se garantizan dos cuestiones esenciales: la coherencia en radiofrecuencia y el sincronismo entre los múltiples canales de datos.

Una vez dentro del FPGA comienza el proceso de formación de los múltiples diagramas direccionales deseados y su canalización para cada receptor. En la Figura 3 se exponen los componentes de la etapa digital del sistema.

En un primer momento se tiene el bloque de configuración de las tarjetas y adquisición de las señales. Como su nombre lo indica cumple con dos misiones esenciales:

La configuración de los receptores de cada ARRadio. Se efectúa con el empleo de un procesador embebido que incluye un canal de comunicación serie SPI en configuración máster capaz de acceder a los registros internos de las dos tarjetas transceptoras a través de los conectores HSMC.

La lógica de control necesaria para separar las muestras de los canales de recepción.

Las señales digitales correspondientes a los cuatro canales de radiofrecuencia pasan al bloque de formación del diagrama direccional donde se crean digitalmente los cinco haces de recepción siguiendo el principio explicado en la sección 2.1. Para obtener cada uno de ellos se tienen como parámetros de diseño la geometría del arreglo de antenas, la frecuencia de trabajo y la dirección del máximo de radiación que le corresponde. Este bloque incluye como paso inicial el proceso de calibración de cada canal de recepción.

Diseño de las etapas de control del receptor y adquisición de las señales

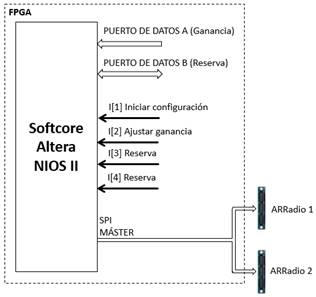

El primer paso para lograr la recepción es configurar los parámetros de los receptores de cada AD9361 mediante la escritura en sus registros internos a través de una línea de comunicación serie SPI procedente del FPGA. Para efectuar este proceso se utilizó el Softcore desarrollado por la empresa Altera NIOS II embebido en el FPGA. La Figura 4 muestra el esquema de conexión empleado.

Su interfaz contiene dos puertos paralelos de 32 bits (A y B) para el intercambio de datos con elementos exteriores al procesador. El primero es un puerto de entrada utilizado para almacenar la palabra de configuración de la ganancia del tracto receptor del sistema. El puerto B presenta la posibilidad de flujo de datos bidireccional y se encuentra de reserva para desarrollos futuros. Cuenta con cuatro entradas de interrupción externaI [1, 2, 3, 4]. La primera interrupción activa la rutina encargada de iniciar la configuración de cada AD9361. Con la segunda se efectúa la modificación de la ganancia según el valor escrito en el puerto de datos A. Las interrupciones I [3] y I[4] permanecen de reserva. El procesador NIOS II incluye como uno de sus periféricos un módulo embebido SPI en configuración de máster encargado de la comunicación con los AD9361 conectados. El sistema diseñado permite direccionar hasta cinco tarjetas transceptoras lo cual brinda cierto grado de escalabilidad al sistema. Como se aprecia en la Figura 4 las líneas de comunicación SPI son enviadas hacia cada ARRadio a través de los conectores HSMC del TR4. Una vez activada la rutina de interrupción I [1] el software interno del procesador efectúa las escrituras correspondientes a la siguiente secuencia de configuración:

Habilitación de los dos canales receptores.

Configuración de los puertos para la transmisión de datos.

Habilitación de la entrada de reloj externa.

Habilitación de la entrada de oscilador local externa.

Establecimiento del ancho de banda del receptor en radiofrecuencia (40 MHz).

Configuración de la frecuencia central de trabajo (2400 MHz).

Configuración de las tasas de muestreo de las señales (40 MHz).

Programación del filtro digital interno.

Configuración del control de ganancia (como manual).

Configuración de la ganancia (60 dB).

Calibración interna del offset de recepción y el balance de los canales en fase y cuadratura (I y Q).

Programación de la máquina de estado interna para establecer el estado de RECEPCIÓN DE DATOS.

Habilitación del sincronismo entre los relojes en todas las tarjetas.

Al concluir este proceso ya es posible iniciar la recepción, sin embargo, las tarjetas no se encuentran sincronizadas aún. Para lograrlo se requieren dos acciones: la distribución de un reloj común hacia los dos ARRadio y la combinación de las escrituras en el registro de configuración del sincronismo multi-chip de cada tarjeta con una activación del terminal SINC conectado a través del HSMC. La secuencia de sincronización es la siguiente:

Habilitación en cada AD9361 la calibración de los PLL (del inglés Phase-Look Table) de banda base.

Aplicar un pulso en el terminal SYNC de forma simultánea a todas las tarjetas.

Deshabilitar la calibración de los PLL y habilitar la calibración de los relojes digitales en cada AD9361.

Aplicar nuevamente un pulso en el terminal SYNC de forma simultánea a todas las tarjetas.

Deshabilitar calibración de los relojes digitales.

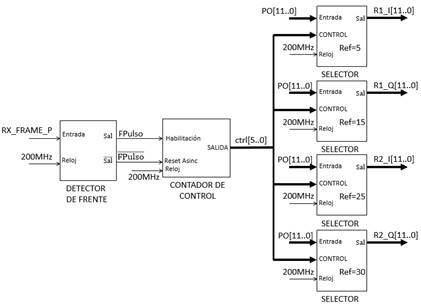

En este punto es posible comenzar la recepción. Los datos digitales llegan al FPGA a través del conector HSMC como parte de un bus de 12 bits en formato complemento a dos y con entrelazamiento de los canales. La tarjeta envía además las señales para la extracción de los datos. En la Figura 5 se muestra el esquema que se emplea para la realización de este proceso en uno de los transceptores.

La señal RX_FRAME_P procedente del AD9361 indica el inicio de cada una de las muestras de la señal a partir de la cual se reciben por P0 [11..0] las componentes I y Q de los receptores 1 y 2 en ese orden. El circuito para la extracción de los datos comienza con un detector de los frentes de subida de RX_FRAME_P (Bloque DETECTOR DE FRENTE). La salida y su componente negada se emplean para habilitar y limpiarde forma asincrónica al CONTADOR DE CONTROL. Este tiene la función de generar las señales necesarias para identificar, dentro del periodo de duración de RX_FRAME_P, la ubicación exacta de las componentes I y Q de las señales recibidas. La salida de control (ctrl [5..0]) es empleada por los cuatro bloques “SELECTOR” con el objetivo de pasar a su salida la señal presente en P0 [11..0] cuando el valor del conteo coincida con el número de referencia (Ref) almacenado en cada uno. De esta forma se logra la separación de las componentes I y Q de cada uno de los canales receptores presentes en el AD9361. Todos los procesos del sistema de control de la recepción operan con un reloj base de 200 MHz. Las señales adquiridas son enviadas hacia los bloques de calibración y seguidamente hacia los formadores del diagrama direccional.

La coherencia en radiofrecuencia se garantiza mediante el empleo de un oscilador local común para todas las tarjetas ARRadio, aplicado por su entrada externa. Esta opción debe estar habilitada y se configura a la frecuencia de trabajo deseada y el oscilador externo debe ser el doble de esta frecuencia y poseer una alta estabilidad.

Procedimiento para la calibración de múltiples canales

La calibración constituye un elemento esencial del sistema. Su realización determina el desempeño del formador digital del diagrama direccional. Como se expresó desde el inicio, en este trabajo se propone un procedimiento basado en la Transformada de Fourier para su implementación. El algoritmo parte de la inyección en cada canal de un tono patrón desplazado 500 kHz por encima de la frecuencia central. Esta señal es procesada y digitalizada por cada integrado de radiofrecuencia y enviada al bloque de calibración. Inicialmente se calcula la Transformada de Fourier de las señales de cada canal y se ubica el punto máximo de cada una. En esta posición se determina la fase a partir de las componentes en fase y cuadratura resultantes de la transformada. Se toma como base el primer canal de recepción y se calcula la diferencia entre las fases correspondientes a cada canal y la referencia.

Para la calibración de amplitud se determina el módulo de las muestras adquiridas en cada canal. Se toma como base al canal con menor nivel de señal y se determina la relación de amplitud entre el resto de los canales y la referencia.

Los valores resultantes de los procesos anteriores son combinados para conformar el peso complejo aplicado a cada línea de recepción para corregir las diferencias existentes entre ellas. El proceso de calibración tiene asociado una serie de controles adicionales necesarios para la generación del tono patrón y su correcta adquisición y procesamiento.

Diseño de las etapas para la formación digital del diagrama direccional

A continuación se muestra el proceso de diseño para la formación digital de uno de los haces. Los restantes constituyen una réplica del mismo modificando únicamente la dirección principal de recepción ( s . El trabajo puede ser dividido en dos etapas fundamentales: diseño del sistema digital en Simulink y exportación a VHDL e implementación del sistema sobre el hardware programable.

El diseño en Simulink cuenta con tres secciones: cálculo de los pesos para cada haz, aplicación de los mismos y la obtención de la señal de salida mediante la suma de los canales digitales.

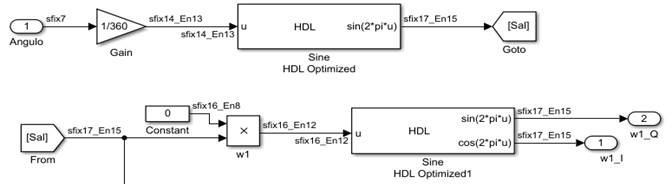

El cálculo de los pesos parte de la implementación de la expresión (2) en función de las características específicas del diseño. En este caso se tiene la realización del procesador para un arreglo de antenas lineal, que trabaja a una frecuencia de 2400 MHz y formado por cuatro antenas separadas a 75 mm. El esquema propuesto se muestra en la Figura 6.

La dirección principal del haz correspondiente se introduce con un formato de 7 bits con signo. La función seno es calculada con el empleo del bloque optimizado para HDL Sine. Previamente el valor del ángulo es acondicionado en el bloque Gain donde es realizada su conversión a radianes y una variación adicional necesaria por las propias características del bloque Sine. Esta etapa es común para todos los canales y se corresponde con el cálculo de sen(

s

en la ecuación (2). La salida del proceso anterior es multiplicada por la constante Constant, cuyo valor varía de un elemento a otro y su amplitud se determina por el factor  . Finalmente es necesario obtener las componentes real e imaginaria del peso. Para ello se emplea el bloque Sine configurado para brindar a su salida tanto el seno como el coseno del valor a su entrada, garantizando su descomposición en fase y cuadratura.

. Finalmente es necesario obtener las componentes real e imaginaria del peso. Para ello se emplea el bloque Sine configurado para brindar a su salida tanto el seno como el coseno del valor a su entrada, garantizando su descomposición en fase y cuadratura.

La aplicación de los pesos es realizada mediante el esquema mostrado en la Figura 7. Recibe a su entrada las componentes en fase y cuadratura de la señal correspondiente al canal correspondiente (En_I y En_Q) y el peso determinado a partir de la dirección de radiación requerida. En su salida se obtiene la multiplicación compleja de ambos datos.

El último paso requiere la combinación lineal de los datos procedentes de los diferentes elementos del arreglo de antenas. Para ello se emplea el esquema mostrado en la Figura 8 compuesto por un sumador de cuatro entradas cuya salida es normalizada con respecto al total de elementos.

En la Figura 8 se puede apreciar la existencia de bloques intermedios para la conversión de datos. El primero se utiliza para limitar la longitud del bus resultante del proceso de la suma. El segundo permite adecuar la salida del procesador a los parámetros de la implementación del sistema. En la imagen solo se muestra el procesamiento de las componentes en fase por lo que debe repetirse para las señales en cuadratura.

Durante la etapa de diseño en Simulink es necesario controlar el crecimiento de los datos con la realización de operaciones matemáticas con el objetivo de evitar la saturación del sistema durante su implementación. En este proceso juegan un papel fundamental los bloques de conversión mencionados con anterioridad.

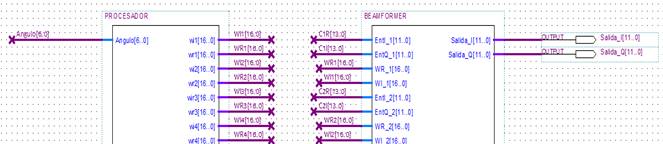

Una vez elaborado y verificado el sistema digital en Simulink es exportado a HDL para la descripción del procesador en el FPGA. Para ello se divide el diseño realizado en dos secciones: la primera está asociada al cálculo de los coeficientes de peso necesarios en función del ángulo de dirección y la segunda incluye el producto complejo de dichos pesos por los canales correspondientes y la posterior combinación lineal de cada una de las líneas de recepción. La Figura 9 muestra una sección de los bloques resultantes en el diagrama esquemático realizado en Quartus II tras el proceso de exportación.

Discusión de los resultados

Con la conclusión del diseño es preciso realizar la verificación y análisis de los principales elementos del sistema. En un primer momento se valoraron los resultados del proceso de calibración debido a su importancia para el proceso de formación del diagrama direccional. La Figura 10 representa las componentes en fase y cuadratura adquiridas por los cuatro canales de recepción. Se puede apreciar la existencia de un desfasaje cercano a 180º, inaceptable para la realización del diagrama direccional. Estas diferencias de fase elevadas son resultado del propio principio de trabajo del AD9361. Entre canales similares de ambas tarjetas el desfasaje no supera los 30º.

Una vez realizado el proceso de calibración, las diferencias de fase obtenidas entre los canales se encuentran por debajo de 0.005º. Este valor no permanece constante y sufre una ligera degradación con el paso del tiempo. Sin embargo, pruebas realizadas tres horas después de iniciado los trabajos arrojan diferencias inferiores a 7º, valores aceptables para el procesamiento digital de los diagramas direccionales. La Figura 11 representa las señales recibidas tras la calibración.

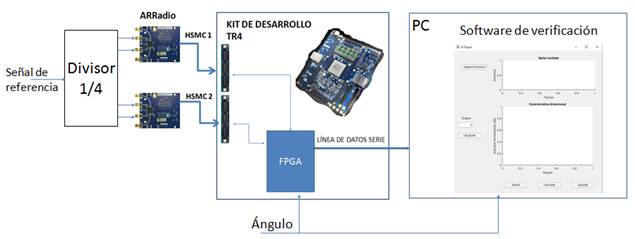

Tras la verificación del estado de calibración entre las líneas de recepción se procede a comprobar la formación digital de la característica direccional del arreglo de antenas. Para ello se inyecta una señal en fase a los cuatro canales de recepción y se varía la dirección de radiación principal en uno de los formadores digitales en el rango de ±60º. Las muestras adquiridas en cada posición son enviadas a través de una interfaz de comunicación serie hacia una PC donde un software desarrollado para la verificación del sistema se encarga de determinar el diagrama direccional normalizado formado digitalmente, a partir de la potencia de las señales en cada sección angular. El esquema empleado para la medición se muestra en la Figura 12.

En la Figura 13 se representa el resultado de una de las mediciones realizadas. En la imagen se observa una respuesta que se corresponde con la característica ideal de la distribución propuesta. La principal afectación del resultado está asociada al nivel de profundidad obtenida en los mínimos del diagrama direccional, los cuales alcanzan el valor máximo de -35 dB. Esto afecta la posibilidad de obtener niveles de lóbulos secundarios inferiores a este valor. La principal causa de estos valores es la influencia de los errores de amplitud y fase posteriores a la calibración, resultado del propio trabajo de los transceptores. Sin embargo, al ser una fuente de error aleatoria no correlacionada, el empleo de un mayor número de canales puede reducir este valor y mejorar el rendimiento del sistema [22].

La Figura 14 muestra la representación gráfica de los múltiples diagramas realizados con el empleo de técnicas de procesamiento digital. Los diagramas se encuentran interceptados al nivel de media potencia y permiten cubrir un sector angular de 90º.

Conclusiones

El sistema implementado garantiza la formación de múltiples diagramas direccionales simultáneos de recepción en banda S y da cumplimiento al objetivo trazado. Su desarrollo brinda una línea tecnológica para la obtención de arreglos de antenas con formación digital de múltiples diagramas direccionales simultáneos.

En el documento se exponen las principales contribuciones del trabajo al mostrar el proceso de configuración y control del transceptor integrado AD9361 mediante el empleo de FPGA. Fueron expuestas las cuestiones esenciales del diseño en Simulink del bloque de procesamiento para la formación digital de la característica direccional. Se obtuvo un procedimiento de calibración con la aplicación de la Transformada de Fourier para la determinación de las diferencias de fase entre los canales de recepción. Se realizó la implementación en FPGA del formador del diagrama direccional, verificado mediante las mediciones de la característica direccional formada digitalmente.

También se logró un procedimiento para la comprobación del diagrama direccional realizado digitalmente, de utilidad para analizar el comportamiento espacial del arreglo de antenas.