Introducción

La utilización de redes de comunicaciones inalámbricas con características directivas constituye una arista en el desarrollo de las telecomunicaciones modernas [1]. Concentrar la energía en la dirección deseada mejora la calidad de la recepción, reduce el efecto de señales interferentes, eleva la seguridad en el flujo de información, facilita la coexistencia espacial con otros sistemas y permite un empleo más eficiente del espectro radioelectrónico [2, 3]. En los últimos años varias aplicaciones inalámbricas han asumido el empleo de antenas directivas: telefonía móvil [4, IEEE 802.11 [5, 6], circuitos de geolocalización [7, 8].

Los diagramas de radiación estrechos, inherentes a estos sistemas, hacen necesario la obtención de un medio para su orientación, adquisición de las señales y seguimiento de estas para mantener la conectividad [9]. Este tema ha sido tratado por diferentes autores que ofrecen soluciones que van desde seguimiento por conmutación de haces [10], hasta máquinas de aprendizaje automático [11]. Una opción recurrente es la utilización de sistemas monopulso. Aunque el origen de esta técnica de seguimiento angular se remonta a los sistemas de radar, su empleo actual se consolida y extiende hacia las telecomunicaciones [12, 13, 14, 15].

Un sistema monopulso típico incluye dos antenas idénticas separadas a determinada distancia (monopulso con comparación de fase) o ubicadas en el mismo centro de fase, pero con la dirección de radiación principal inclinada (monopulso con comparación de amplitud). La salida de ambas antenas es sumada para obtener un diagrama suma (Σ) y restadas para el diagrama diferencia (Δ). El procesamiento de estos canales permite estimar la desviación de las señales incidentes con respecto a la dirección axial del conjunto [16]. Diversos autores abordan elementos del desarrollo de sistemas con monopulso. Sus trabajos se centran en dos líneas fundamentales: estudios teóricos sobre su rendimiento [17, 18, 19] y diseño de dispositivos de antenas y alimentadores [20, 21, 22].

El objetivo de este trabajo es mostrar la implementación de los bloques para la estimación de la desviación angular en un sistema monopulso con comparación de amplitud a partir de las señales en fase y cuadratura de los canales suma y diferencia. Como plataforma de procesamiento se emplea el FPGA de la familia Stratix IV integrado en la placa de desarrollo TR4. Durante el diseño se utiliza la herramienta de simulación multidominio Simulink para la obtención de los códigos de descripción de hardware necesarios en la implementación. El sistema propuesto es validado con un arreglo de antenas lineal de seis elementos con formación digital de los diagramas Σ y Δ.

El trabajo está formado por tres secciones. En la primera son abordados temas relacionados con los principios de funcionamiento de los sistemas monopulso, así como los elementos matemáticos fundamentales que intervienen en el procesamiento de las señales de los canales suma y diferencia. A continuación, se analiza el desarrollo de sistemas digitales con el empleo de FPGA y la utilización del Matlab para la creación de códigos en lenguajes de descripción de hardware (HDL, por sus siglas en inglés) sintetizables. En un segundo momento se explica la estructura general del sistema propuesto y se aborda su funcionamiento. También se detallan los bloques y esquemas desarrollados para obtener la desviación angular a partir de las señales de los canales suma y diferencia.

A partir de la bibliografía consultada se consideran como probables contribuciones de esta investigación: la fundamentación matemática del procesamiento monopulso con señales en cuadratura, el diseño en Simulink del procesador para un sistema con monopulso, análisis de la obtención de la curva de error basado en modelos polinomiales y la implementación en FPGA del estimador de desviación angular con monopulso. Adicionalmente, se logra la verificación del sistema diseñado a partir de la formación digital de los canales suma y diferencia de un arreglo lineal compuesto por ocho antenas.

Materiales y métodos

Principios de un sistema monopulso

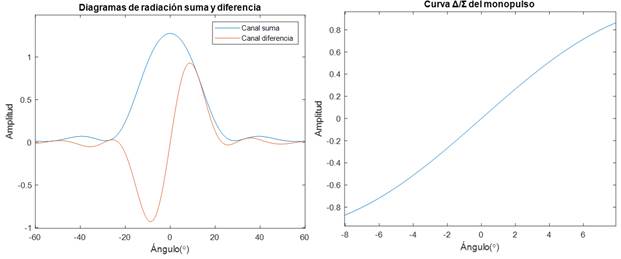

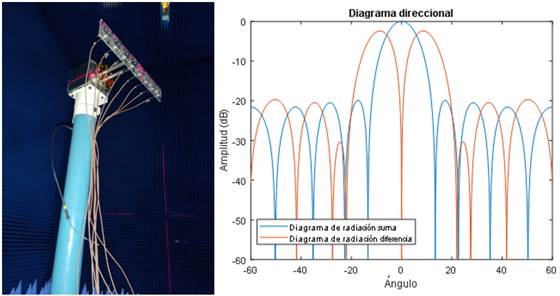

La estimación angular de la dirección de fuentes de señales a través del monopulso con comparación de amplitud parte de poseer dos diagramas de radiación con igual centro de fase y una desviación en su orientación con respecto al eje axial del sistema. La suma y resta de ambos conducen a las respuestas mostradas en la Figura 1.

La línea azul representa al canal Σ, la roja se corresponde con el Δ, el eje de las abscisas contiene la dirección angular en grados y el de las ordenadas la amplitud de las respuestas. Si se tiene una fuente de radiofrecuencia transmitiendo desde la dirección normal (0°), la salida del canal suma es máxima mientras que en el canal diferencia no se obtiene señal. Si la fuente sufre un desplazamiento de su posición actual, la respuesta del canal diferencia deja de ser nula, surge un voltaje, denominado voltaje de error, que puede ser utilizado para estimar la magnitud del desplazamiento. Adicionalmente, Δ presenta fases contrarias alrededor de 0° lo cual posibilita conocer el sentido del movimiento. Lo anterior constituye el principio de trabajo de un sistema monopulso para la estimación de la posición angular de fuentes de radiofrecuencia.

Procesar solo el canal diferencia crea una dependencia entre la magnitud del voltaje de error y la amplitud de las señales recibidas. Para erradicar esta deficiencia se trabaja con la curva Δ/Σ para obtener la señal de error (Error); de esta forma, además de solventar la problemática expuesta se logra mayor linealidad en el comportamiento del error en función del ángulo de incidencia. La imagen de la derecha en la Figura 1 representa la característica Δ/Σ en el sector angular comprendido en el ángulo de radiación del canal suma, sección utilizada para el procesamiento monopulso. Como se observa, a cada valor de corrimiento angular le corresponde un nivel de error, entre estos existe una relación aproximadamente lineal caracterizada por la función Δ/Σ.

En la mayor parte de los trabajos consultados los diagramas de radiación suma y diferencia son generados de forma analógica a través de la disposición de las antenas y su sistema de alimentación [19]. Esta arquitectura permite obtener el corrimiento angular de las señales recibidas con respecto al eje axial del sistema en el plano sobre el cual ocurre la desviación de los diagramas de radiación por lo que se considera de una dimensión. Para lograr un sistema monopulso de dos dimensiones es necesario agregar dos diagramas de radiación en el plano perpendicular al anterior [23]. El presente trabajo se centra en el desarrollo del procesamiento de una dimensión al ser la base de todo sistema monopulso.

Procesamiento de los canales suma y diferencia

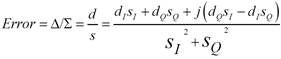

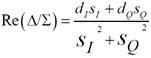

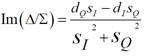

El procesador de un sistema monopulso trabaja con la relación entre las señales de salida de los canales diferencia y suma (d y s respectivamente). Los fasores de voltaje (envolventes complejas) de ambas señales pueden ser denotados en función de sus componentes en fase y cuadratura mediante las expresiones 1 y 2 respectivamente:

En las expresiones 1 y 2 los subíndices I y Q se refieren se refieren a la parte real e imaginaria (en ese orden) de las señales d y s.

A partir de estas, la relación compleja entre los canales Δ y Σ queda definida como (3):

Esta puede ser descompuesta en sus componentes ortogonales (4 y 5):

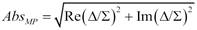

El valor absoluto de Δ/Σ (Abs MP ) contiene la información necesaria para determinar la desviación de la fuente de la señal recibida con respecto al origen y su fase (Fase MP ) indica el sentido de la desviación [24]. El subíndice MP indica que ambos se obtienen a la salida del procesador monopulso. Pueden ser calculados mediante las expresiones 6 y 7 respectivamente.

Procesador digital de sistemas monopulso sobre fpga

Los FPGA son dispositivos lógicos programables que se emplean en un gran número de aplicaciones de procesamiento digital de señales. Si bien operan a frecuencias de reloj más bajas y tienen picos de rendimiento inferiores en comparación con otros dispositivos como son los DSP (del inglés Digital Signal Processor) o unidades de procesamiento central (CPU), la posibilidad de adaptarse para cada aplicación particular le permite a los FPGA lograr mejores tasas de rendimiento en muchas de estas aplicaciones [25].

En los procesadores monopulso se requiere una elevada precisión durante la realización de las diferentes operaciones matemáticas que intervienen en la estimación. Debe ser sensible a pequeños valores de error para asegurar una mayor precisión en el seguimiento y reaccionar de forma satisfactoria a desviaciones angulares pequeñas. En este sentido, el empleo de dispositivos optimizados para la realización de operaciones en punto flotante representa la mejor opción en comparación con los FPGA. A pesar de ello, el procesamiento adecuado de señales en punto fijo permite obtener índices de calidad adecuados en una amplia gama de aplicaciones lo cual brinda a los FPGA la posibilidad de ser utilizados en sistemas de procesamiento digital de señales donde se requiera de precisión durante la realización de operaciones matemáticas.

En el presente trabajo se efectúa la implementación de los bloques que intervienen en el procesamiento de las señales adquiridas por un sistema monopulso utilizando un FPGA. Para la descripción del hardware del procesador se optó por un flujo de diseño basado en la Plataforma de Simulación Multidominio Simulink integrada en el Matlab [26]. El procedimiento parte de la realización de los componentes del sistema digital Simulink y su exportación a lenguaje de descripción de hardware. Mediante la instrucción hdllib se accede a los bloques que forman parte de la librería de elementos sintetizables a HDL del Simulink, con estos es posible elaborar un diseño íntegro del sistema capaz de ser exportado y utilizado en aplicaciones prácticas con dispositivos de hardware programables. Simulink no solo permite el diseño del sistema sino además incluye los elementos necesarios para su verificación funcional y la herramienta HDL Coder Properties para configurar las propiedades del código generado por cada bloque. Entre sus posibilidades de configuración se encuentran la selección del dispositivo sobre el cual se sintetizará el diseño y la frecuencia de trabajo máxima del bloque, opciones del pipeline y el sistema de sincronismo, manejo de las operaciones en punto flotante y generación de banco de pruebas. En las etapas de diseño se debe valorar constantemente la precisión de las operaciones matemáticas que se realizan en punto fijo y evitar el desbordamiento de los datos durante estas, ambas situaciones influyen negativamente en el rendimiento del sistema. Para el desarrollo del procesador monopulso el primer elemento tiene un peso fundamental debido a la precisión exigida durante el manejo de los datos.

El esquema sintetizado mediante este procedimiento tiene la ventaja de poder ser empleado en cualquier familia de dispositivos FPGA. En el presente trabajo se escogió como plataforma de procesamiento el dispositivo EP4SGX230C2 presente en la tarjeta de desarrollo Terasic TR4. Este incluye 228000 elementos lógicos, 17133 kb de memoria y 1288 multiplicadores de 18x18 bits. Adicionalmente basado en los desarrollos obtenidos en [27] es posible emplear el mismo diseño para obtener los canales suma y diferencia.

Implementación del procesador monopulso

Esquema general del sistema de procesamiento

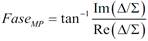

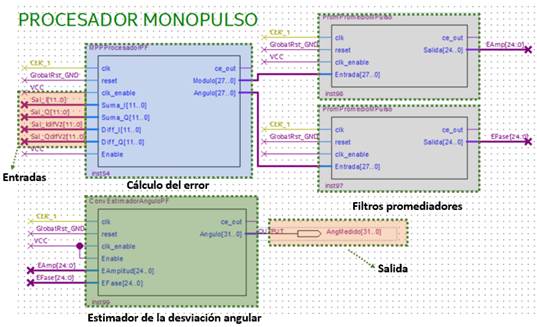

La estimación de la desviación angular a partir de las señales suma y diferencia necesita dos momentos para su realización. Su funcionamiento se puede describir a través del esquema mostrado en la Figura 2.

El primer elemento del sistema es el bloque de cálculo del error. Este recibe a su entrada las componentes en fase y cuadratura de los canales de suma y diferencia y entrega el valor absoluto y el argumento del fasor del error. Su implementación consiste en el desarrollo del conjunto de ecuaciones expuestas en la sección 2.2. La segunda etapa del procesamiento contiene un bloque discriminador, encargado de determinar la desviación angular a partir de la señal de error. Para ello se evalúa el error determinado en la función inversa de Δ/Σ, denominada a partir de ahora como (Δ/Σ)-1.

Diseño del bloque de cálculo del error

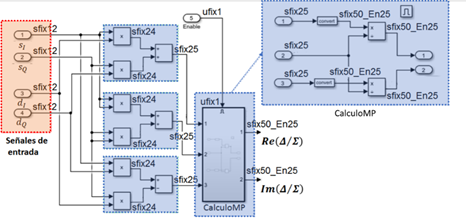

Para la obtención del bloque de cálculo del error se organiza el diseño en dos secciones. La primera, emplea las señales en fase y cuadratura de los canales suma y diferencia para determinar las componentes real e imaginaria de la señal de error, básicamente efectúa la implementación de las ecuaciones 4 y 5. En la segunda sección se desarrollan las expresiones 6 y 7 para obtener el valor absoluto y el argumento del error. El diseño en Simulink de los elementos correspondientes a la primera etapa de cálculo se representa en la Figura 3.

Figura 3 Esquema en Simulink para el cálculo de las componentes en fase y cuadratura de la señal de error.

En la figura se emplean tres notaciones para simbolizar el formato de los datos en las diferentes secciones del sistema: sfixN (valor de N bits en punto fijo con signo y sin bits en la parte fraccionaria), ufixN (valor de N bits en punto fijo sin signo y sin bits en la parte fraccionaria) y sfixN_EnM (valor de N bits en punto fijo con signo y con M bits en la parte fraccionaria). La precisión de cada valor se encuentra determinada por el número de bits empleados en la parte fraccionaria.

Las entradas procedentes de los canales Σ y Δ son combinadas linealmente en tres agrupaciones para resolver los términos del numerador y denominador de las expresiones 4 y 5. Los resultados son enviados al bloque sincrónico CalculoMP donde se efectúan las operaciones finales. Todos los datos manejados se encuentran en punto fijo, lo cual reduce las exigencias del cálculo y ocupación de recursos (con relación al punto flotante) a expensas de afectar la exactitud de los resultados. Los principales problemas surgen durante las divisiones efectuadas en CalculoMP. Para lograr una mejor aproximación se introducen bloques de conversión de datos que agregan 25 bits en la fracción de los dividendos. En principio, estos bloques modifican únicamente la representación de las señales de entrada, sin embargo, su empleo permite que la salida de las divisiones pueda configurarse de igual forma con 25 bits en la fracción del cociente limitando el error absoluto máximo del cálculo a 1.49x10-8.

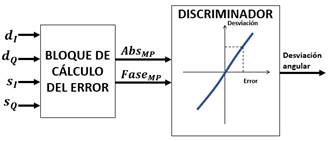

Para la segunda etapa de cálculo se utilizó el esquema mostrado en la Figura 4. Tiene como entradas las componentes real e imaginaria del error. Estas son procesadas por dos líneas independientes para determinar el valor absoluto y el argumento de la señal de error. Las principales operaciones de este esquema se efectúan en punto flotante de simple precisión, lo cual se denota en la figura con el identificador single, se utiliza single(c) para datos complejos en igual formato. El trabajo en punto flotante es necesario debido a restricciones del Simulink para la exportación a HDL de los bloques atan2 y |u| con señales en punto fijo.

Los primeros elementos del procesamiento son dos conversores de datos para ajustar las señales de entrada (palabras de 28 bits con 23 en la fracción) a las exigencias del diseño. Tras la modificación, Re(Δ/Σ) y Im(Δ/Σ) pasan a los diferentes canales de cálculo. La línea superior realiza la implementación de la ecuación 6, para ello construye un número complejo con las partes real e imaginaria y determina su módulo. Para el cálculo del argumento se dificulta la realización de un procedimiento similar por lo que se desarrolla el esquema mostrado en la línea inferior. Los valores angulares brindados por atan2 toman valores entre -π y π lo cual dificulta la toma de decisión sobre el sentido del movimiento en las proximidades de π. Para solventar el problema se efectúa una traslación en π/2 del valor modular del ángulo determinado. Finalmente, los valores calculados son convertidos en punto fijo para las siguientes etapas de procesamiento.

Diseño del bloque discriminador

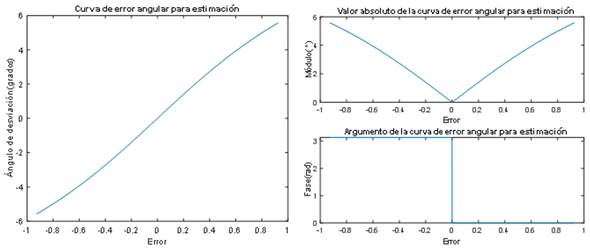

El bloque discriminador de un sistema monopulso opera directamente con la señal de error para obtener la desviación angular del objetivo mediante la evaluación de Abs MP y Fase MP en (Δ/Σ)-1. La Figura 5 contiene la modelación de la curva (Δ/Σ)-1 de un arreglo lineal uniforme de 8 elementos separados 0.65 veces la longitud de onda trabajo, se representan además su valor absoluto y argumento.

Se observa que para todo valor de Error se cumple que (Δ/Σ)-1(Error)= (Δ/Σ)-1(Error), esto permite afirmar que su valor modular se corresponde inequívocamente con un valor modular en la desviación de las señales recibidas con respecto al eje de radiación normal. La fase sufre un cambio de 180° de un sector a otro lo que permite caracterizar la dirección de la desviación. Para la implementación del bloque discriminador debe evaluarse Abs MP en la curva descrita en el primer cuadrante de (Δ/Σ)-1 y agregar el sentido de la desviación a partir de Fase MP .

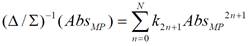

El primer paso para obtener el discriminador es determinar la ecuación matemática que describe a la función (Δ/Σ)-1. Esta depende directamente de la forma de los diagramas de radiación Σ y Δ. Una aproximación útil se desarrolla en el trabajo realizado por Plessis [28], basada en el empleo de modelos polinomiales. A partir de ella es posible establecer la siguiente expresión para caracterizar la desviación angular a partir del módulo del error:

El índice n toma valores enteros positivos hasta N y 2N+1 caracteriza el grado del polinomio utilizado. La expansión en series de Taylor dada permite únicamente los términos con exponentes impares, los coeficientes de estos se denotan k 2n+1 . Por la simplicidad del cálculo es ampliamente utilizada la aproximación lineal de la curva para la cual N=0, a pesar de ello incrementar un término permite reducir los errores durante la determinación de la desviación angular [28]. En este caso la expresión 8 queda redefinida como:

El segundo elemento del discriminador es determinar la dirección de la desviación angular, para ello se realiza un esquema de comparación con el empleo de Fase MP . Como resultado de la comparación se ajustará el signo del valor angular determinado a partir de la ecuación 9.

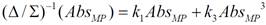

La Figura 6 muestra el esquema en Simulink propuesto para el discriminador. En esta se incluyen los bloques implementados en Simulink para la obtención de la desviación angular a partir de los valores de Abs MP y Fase MP . La representación del formato de los datos conserva la nomenclatura empleada en las figuras 3 y 4.

Aunque la medición de la desviación angular en un sistema monopulso solo necesita un instante de muestreo para efectuar el cálculo, la presencia de ruido en los canales suma y diferencia puede afectar el valor de la estimación. Por tanto, el primer bloque del discriminador propuesto es un filtro promediador. En este se determina el valor medio de 20 muestras consecutivas de Abs MP y Fase MP para reducir el error debido al ruido no correlacionado. Los valores resultantes son enviados a Estimador Angulo PF donde se determina el corrimiento angular. Este bloque se encuentra formado por dos subsistemas: el subsistema 1, encerrado entre puntos rojos, realiza la implementación de la ecuación 9, tiene como entradas el módulo del error determinado y las constantes k 1 y k 3. El subsistema 2 se encarga de incorporar el signo al valor de la desviación, para ello incluye un multiplexor que direcciona hacia la salida (Δ/Σ)-1(Abs MP ) o -(Δ/Σ)-1(Abs MP ) en función del signo de Fase MP . El último elemento convierte el ángulo resultante a punto flotante con simple precisión.

Implementación del sistema de procesamiento

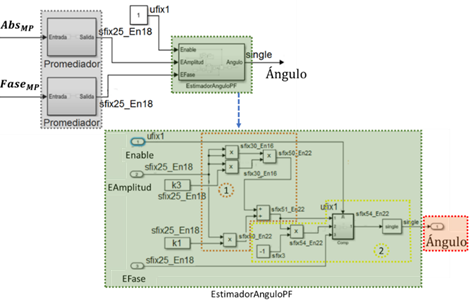

Una vez elaborado y verificado el sistema digital en Simulink es exportado a HDL para la descripción del procesador en el FPGA. El diseño efectuado es agrupado en tres grupos para su exportación: el primero incluye los bloques para la determinación de Abs MP y Fase MP , el segundo está compuesto por el filtro promediador y por último el bloque EstimadorAnguloPF. Tras la obtención de los códigos sintetizables estos son utilizados para la descripción esquemática de hardware del procesador monopulso. La Figura 7 contiene una captura de la descripción realizada en Intel Quartus Prime Standard Edition.

Discusión de los resultados

Utilización de recursos del procesador monopulso

Un elemento importante tras la implementación es el análisis de la utilización de recursos de hardware. A través de la herramienta Fitter Resource Utilization by Entity presente en Intel Quartus Prime Standard Edition fue posible valorar el total de recursos ocupados por el procesador monopulso diseñado. Los resultados se reflejan en la Tabla 1.

Tabla 1 Resumen de utilización de recursos de hardware por el procesador monopulso

| Función | Filtros promediadores (2) | Estimador del ángulo | Cálculo del error |

|---|---|---|---|

| Nombre en el diseño esquemático | PromPromedioMPulso | ConvEstimadorAnguloPF | MPPProcesadorPF |

| Lógica utilizada por bloques funcionales | 1380 | 710 | 13316 |

| Lógica total utilizada | 15406 | ||

El diseño empleó un total de 15406 elementos lógicos, lo que representa un 6.75% del disponible en el FPGA utilizado. El mayor peso estuvo en los bloques para el cálculo del error. En estos se realizan la mayor parte de las operaciones del procesamiento, incluye el manejo de datos en punto flotante con simple precisión y punto fijo, además presenta operaciones complejas como el cálculo de la tangente inversa. El sistema implementado aún puede ser optimizado en cuanto a la utilización de recursos. Entre las opciones para hacerlo se encuentran reducir la precisión de las señales en punto fijo, disminuir el total de muestras en el cálculo del promedio o utilizar la aproximación lineal de la curva (Δ/Σ)-1. Todo ello implica un deterioro en el rendimiento procesador monopulso. Lo anterior conlleva a una relación de compromiso entre el costo en recursos y la precisión en la estimación de la desviación angular.

Comprobación funcional del procesador monopulso

Para la comprobación funcional del sistema de procesamiento diseñado se utilizó un arreglo lineal uniforme de ocho antenas con una separación de 8.125 cm en la banda de 2.4 GHz. En la formación de los canales de suma y diferencia se aplicaron técnicas de procesamiento digital a las señales recibidas por cada uno de los elementos. Los diagramas de radiación Σ y Δ se formaron digitalmente mediante las distribuciones de amplitud Taylor y Bayliss respectivamente, ambas con -20 dB en el nivel de los lóbulos laterales. La Figura 8 muestra una imagen de la antena utilizada durante las pruebas en cámara anecoica y los diagramas de radiación formados digitalmente para el sistema de estimación angular con monopulso.

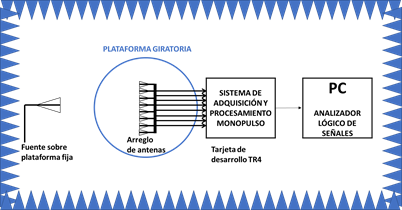

El diseño de las etapas de adquisición, digitalización de las señales del arreglo de antenas y formación digital de los diagramas de radiación se efectuó con un esquema similar al desarrollado en [27]. Emplear la placa de desarrollo TR4 posibilitó integrar en la misma plataforma la obtención de los canales suma y diferencia, y el procesador monopulso. El esquema utilizado para la medición se muestra en la Figura 9.

En una posición fija se ubicó la antena transmisora, el sistema de antenas con monopulso se colocó en la plataforma giratoria de la cámara anecoica. Se realizaron variaciones controladas en la posición de la plataforma giratoria causando una desviación en la dirección de la señal incidente sobre el arreglo. A través del analizador lógico de señales de Intel Quartus Prime Standard Edition se verificó la correspondencia entre la magnitud y sentido del movimiento realizado y el ángulo entregado a la salida del procesador monopulso diseñado.

Durante las mediciones fueron verificadas fuentes de señal provenientes de 11 posiciones angulares distribuidas en un sector angular de ±2.0° y con tres valores de relación señal a ruido diferentes (56, 48 y 38 dB). Para cada una de las 33 comprobaciones efectuadas se tomaron con el analizador lógico de señales 1023 muestras del ángulo estimado.

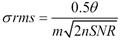

En correspondencia con las fuentes consultadas relacionadas con la implementación de procesadores monopulso, la raíz del error medio cuadrático del ángulo medido (σrms) permite valorar el comportamiento del estimador angular para diferentes configuraciones del sistema [13, 16, 18, 24, 29]. En la expresión 10 se define la dependencia de este con el ángulo de radiación del canal suma (ϴ), la relación señal a ruido en veces (SNR), la pendiente de la curva Δ/Σ (m) y el número de muestras de señal recibidas (n) [30].

La Tabla 2 muestra un resumen del comportamiento de la raíz del error medio cuadrático tras procesar los datos adquiridos.

Tabla 2 Raíz del error medio cuadrático del ángulo estimado por el procesador monopulso

| Posición angular de la fuente de señal (0) | Raíz del error medio cuadrático (0) | ||

|---|---|---|---|

| SNR=56dB | SNR=48dB | SNR=38dB | |

| -2 | 0.00581248655912425 | 0.0234098269963706 | 0.0556776436283002 |

| -1.5 | 0.00936311913840682 | 0.0145481957644238 | 0.0469041575982343 |

| -1 | 0.00901315704955816 | 0.00922030368263432 | 0.0400000000000000 |

| -0.5 | 0.00436577599058862 | 0.0102829956724682 | 0.0400000000000000 |

| -0.1 | 0.00130479883506999 | 0.00546159317415715 | 0.0424264068711929 |

| 0 | 0.00355161934897309 | 0.0331662479035540 | 0.0500000000000000 |

| 0.1 | 0.00240848500099129 | 0.00608678897284931 | 0.0346410161513775 |

| 0.5 | 0.00181237413356073 | 0.00732195329130144 | 0.0360555127546399 |

| 1 | 0.00726333256845644 | 0.00926169530917531 | 0.0360555127546399 |

| 1.5 | 0.00770707467201402 | 0.00476098729256863 | 0.0331662479035540 |

| 2 | 0.00239463984765977 | 0.00631078442033952 | 0.0228606649072156 |

| Valor medio | 0.0050 | 0.0118 | 0.0398 |

| Valor esperado | 0.0043 | 0.0108 | 0.0343 |

En la sección inferior de la tabla se muestra el valor medio de la raíz del error medio cuadrático del ángulo estimado para cada relación señal a ruido. El cálculo de σrms en las diferentes posiciones se efectuó a partir de los 1023 valores angulares estimados para cada una. El valor esperado se obtuvo de la aplicación de la expresión 10 para el sistema bajo análisis: con la geometría y distribución de amplitud propuesta para el arreglo de antenas se tiene un ángulo de radiación de 7.34° y una pendiente de 0.2131, el número de muestras de la señal toma el valor de 20 en correspondencia con los filtros promediadores incorporados.

La mitad del ángulo de radiación del arreglo de antenas constituye el máximo valor de σrms que se puede obtener durante la estimación de la dirección angular de una señal que arriba por el lóbulo principal de la antena [24]. Determinar la relación porcentual entre los valores del error obtenidos y el máximo error posible brinda una idea precisa del comportamiento del sistema diseñado. La Tabla 3 muestra los resultados de dicha operación.

Tabla 3 Porciento del error en la medición de la coordenada angular

| 0.034 | 0.081 | 0.271 | |

| 0.029 | 0.074 | 0.233 | |

| 0.005 | 0.007 | 0.038 | |

Los resultados muestran que existe correspondencia entre el rendimiento del sistema monopulso ideal y el diseñado, las diferencias entre ambos no superan el 0.038%. En todos los casos la raíz del error medio cuadrático medido es inferior a 0.3% del máximo error posible, lo cual garantiza la realización de mediciones con una precisión de 0.0110.

Conclusiones

A lo largo del trabajo se muestran los elementos considerados durante la implementación de los bloques para la estimación de la desviación angular en un sistema monopulso con comparación de amplitud a partir de las señales en fase y cuadratura de los canales suma y diferencia, por lo que se da cumplimiento al objetivo trazado. Su desarrollo brinda una solución para el procesamiento monopulso basado en FPGA.

En el documento se exponen las principales contribuciones del trabajo al aplicar la fundamentación matemática del procesamiento monopulso para señales en fase y cuadratura procedentes de los canales Σ y Δ. Sobre la base de estas fue diseñado en Simulink el procesador para un sistema con monopulso y se efectuaron los análisis pertinentes para la obtención de la curva de error basado en modelos polinomiales. El diseño final del estimador de desviación angular con monopulso fue exportado a lenguaje de descripción de hardware e implementado en un FPGA.

Las pruebas funcionales realizadas permitieron validar el sistema a través de un arreglo lineal compuesto por seis antenas. Mediante técnicas de procesamiento digital se formaron los diagramas de radiación suma y diferencia y en el interior de una cámara anecoica se comprobaron los resultados de la estimación de la desviación angular de las señales incidentes sobre el arreglo de antenas. Como resultado de las mediciones efectuadas se determinó la correspondencia entre el sistema diseñado y los límites teóricos establecidos para este, la diferencia entre ambos no supera el 0.038%. El caso más crítico se obtuvo para una relación señal a ruido de 38 dB para la cual se garantiza una precisión de 0.011° durante la medición de las coordenadas angulares de las fuentes de señal incidentes. Como se aprecia en la expresión 10, y los resultados obtenidos existe una relación inversa entre la relación señal a ruido y la raíz del error medio cuadrático, por lo que se recomienda analizar en trabajos futuro el comportamiento del procesador diseñado en condiciones de baja relación señal a ruido.

El procesador monopulso implementado en combinación con el sistema de antenas adecuado puede ser utilizado como parte de una red de comunicaciones inalámbricas con características directivas. En esta, el ángulo resultante de la estimación puede indicar la dirección de radiación principal para redirigir el diagrama direccional de las antenas, o puede tomarse como señal de estímulo para un sistema de control automático que efectúe el seguimiento de la fuente de señal deseada.