Mi SciELO

Servicios Personalizados

Revista

Articulo

Indicadores

-

Citado por SciELO

Citado por SciELO

Links relacionados

-

Similares en

SciELO

Similares en

SciELO

Compartir

Ingeniería Electrónica, Automática y Comunicaciones

versión On-line ISSN 1815-5928

EAC vol.33 no.2 La Habana Mayo-ago. 2012

Diseño FPGA de un modulador DTMB para canalización de 6MHz

FPGA design of DTMB modulator for 6MHz bandwidth

Ing. Nelson García Rodríguez, Ing. Addis Rey Domínguez, Ing. Luis Giraldo Raymond Rodríguez

Departamento de I+D deLACETEL, CUBA, nelson@lacetel.cu, 683-2824

RESUMEN

El presente trabajo describe el proceso de diseño de un modulador de TV digital, de acuerdo a las especificaciones del estándar DTMB. El diseño contempla la adaptación para una trama de canal de 6MHz; se realiza sobre plataforma FPGA empleando como herramientas el System Generator e ISE de Xilinx, y MATLAB y Modelsim para el modelado y verificación funcional.

Palabras claves: DTMB, modulación, FPGA, Xilinx.

ABSTRACT

The present paper describes the design of a digital TV modulator, according with the specifications of DTMB standard. The design is made for 6 MHz channel frame, over FPGA platform with Xilinx System Generator and ISE as design tools, Modelsim and MATLAB for simulation.

Key words: DTMB, modulation, FPGA, Xilinx.

INTRODUCCION

Las dificultades a las que Cuba se tiene que enfrentar para cambiar a la Televisión Digital Terrestre (TDT) son grandes y numerosas, pero el cambio es inevitable. Mientras más demore, más difícil será después, porque habrá que hacerlo todo en plazos más apretados 1.

Cuba ha dado los primeros pasos para la adopción de uno de los estándares tecnológicos para la TDT, realizando pruebas de campo sobre las 4 normas vigentes. (Habana 2007 y 2009).

La norma DTMB2 (Digital Terrestrial Multimedia Broadcast) se usa principalmente en China y está en prueba en otros países. En estos momentos, las comisiones designadas por el gobierno cubano están considerando seriamente su adopción, pues los resultados de pruebas comparativas realizadas en todo el mundo la señalan como la más completa técnicamente: además de las pruebas realizadas en la Habana, también se han realizado en Beijing, Caracas, Lima y Quito. Debido a que fue la última norma en ser lanzada, ha incorpora los más novedosos algoritmos y reutiliza lo mejor de cada una de las que la antecedieron.

Más allá de que los estándares de TDT están compuestos por numerosos documentos, el elemento principal de la norma es aquel donde se describe al proceso de modulación de la señal y se especifican sus características técnicas, tema en el cual se centra este artículo.

Debido al número relativamente pequeño de moduladores en las cadenas de transmisión de la TV, aun en los países más extensos territorialmente, no es factible económicamente la producción de ASIC para realizar la modulación. Por otra parte, la velocidad requerida para el procesamiento de la información requiere en muchos casos el empleo de estructuras de hardware dedicadas. Estas 2 razones determinan que los moduladores para TDT sean desarrollados actualmente sobre tecnología FPGA.

En el presente trabajo se proponen variantes de implementación para los principales módulos que intervienen en el proceso de modulación de una señal DTMB. Los resultados son comprobados mediante simulación aprovechando las potencialidades de integración de herramientas de descripción de hardware del System Generator de Xilinx, con MATLAB Simulink.

DISEÑO PROPUESTO

Elementos generales

En la figura 1 se muestra un esquema en bloques del modulador DTMB, tomando como punto de partida una trama codificada MPEG-2, H.264 o AVS.

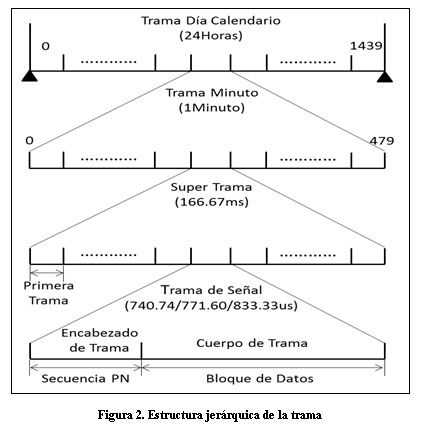

La Trama de Señales la unidad básica en la estructura de tramas (figura 2). Una Trama de Señal está compuesta por 2 partes en el dominio de la señal en el tiempo, el Encabezado de Trama y el Cuerpo de Trama.

La razón de símbolo en banda base para el Cuerpo y el Encabezado es la misma. Como en Cuba el ancho de banda es de 6MHz, la razón de símbolos pasa a ser 5.67MHz, produciéndose una reducción de la carga útil a transmitir (en una razón 3/4), en comparación con los 7.56MHz que establece la norma para un ancho de banda de 8MHz. La estructura de trama, sincronización, modulación, estimación de canal y corrección de errores son compatibles tanto en sistemas de 6MHz como en 8MHz 3.

El Cuerpo consta de 3744 símbolos de datos y 36 símbolos de información de sistema para un total de 3780 símbolos y una duración de 666.67us, o sea, 3780/5.67M. El Encabezado puede tomar tres longitudes mientras que el Cuerpo tiene un período de tiempo fijo, en todas las opciones de encabezado debe cumplirse que la razón de símbolos sea 5.67MHz.

Las características de cada uno de los bloques ilustrados en la figura 2 y las implementaciones propuestas serán descritas a continuación.

Dispersor de Energía

Los datos son aleatorizados mediante multiplicación por una secuencia binaria pseudo-aleatoria de orden 15 (PRBS-15). El propósito de esta operación es eliminar todo sesgo estadístico que la secuencia de datos de la fuente pueda tener. Por ejemplo, varios cuadros sucesivos de una imagen negra podrían, según como haya sido hecha la codificación de los datos de entrada, generar un flujo de transporte en el que una gran mayoría de bits consecutivos sean ceros o unos. Puesto que el resto de la cadena de codificación y modulación es determinística, ello finalmente se traduciría en una transmisión con características espectrales desbalanceadas 4.

La secuencia pseudo-aleatoria se construye a base de un de registro de desplazamiento con realimentación lineal o LFSR (siglas en inglés de Lineal Feedback Shift Register), como se propone en la figura 3.

Un LFSR es un registro de desplazamiento cuya entrada es una función lineal de su estado anterior. La función lineal que utiliza es un OR exclusivo, así la entrada es manejada por esta operación lineal en la que intervienen varios elementos del registro.

La salida del generador PRBS será aplicada al flujo de bits de entrada mediante una operación XOR para aleatorizar los datos.

Corrector de Errores Progresivo

Los sistemas de TDT implementan la codificación del canal con protección contra errores mediante dos códigos correctores. En el sistema DTMB son ambos códigos de bloques, el código externo es BCH (Bose-Chaudhuri-Hocquenghem ), y el interno es un código LDPC (Low Density Parity Check o Chequeo de Paridad de Baja Densidad).

El código BCH tiene 2 propósitos. El primero es adaptar la tasa de datos de entrada MPEG2 a las palabras LDPC según sus 3 posibles modos de trabajo. El otro propósito es reducir el umbral de error del sistema, mediante la corrección de errores esporádicos del codificador interno, en la forma de corrección de un error simple o detección de uno doble 5.

El codificador externo es del tipo BCH (762,752) correspondiente a 752 bits de información y 10 de chequeo; este se obtiene del código BCH (1023,1013), mediante la inserción de 261 ceros a los bits de información. Una Trama de Transporte MPEG-2 contiene 188 Bytes o lo que es lo mismo 1504 bits. La codificación BCH se efectuará sobre 752 bits correspondientes a la mitad de dicha Trama de Transporte.

La norma describe el polinomio generador que establece las palabras válidas del código según la ecuación GBCH(x)=1+x3+x10. El mismo es una subclase de los códigos cíclicos, que puede ser fácilmente implementado con registros de desplazamientos realimentados, lo cual disminuye sustancialmente la complejidad del hardware. Para realizar el diseño del BCH se debe efectuar la división polinomios a base de estos LFSR. Además, para formar la palabra de código de forma sistemática se requiere de un circuito conmutador (multiplexor) que alterne entre bits de mensaje y de chequeo.

Luego de la codificación BCH, los datos son entregados al codificador LDPC, correspondiente al FEC interno de la norma DTMB. Las tres razones de código que utiliza el FEC son 0.4, 0.6 y 0.8 y están dadas por la cantidad de grupos de bits codificados BCH que tienen que concatenarse para entrar al codificador LDPC.

Los códigos de chequeo de paridad de baja densidad son una clase de códigos de bloques lineales, los cuales alcanzan un desempeño cercano al límite teórico máximo o límite de Shannon para bloques de transmisión extensos. Su descripción e implementación hardware se realiza mediante matrices de chequeo esparcido 5.

Para el diseño del codificador LDPC se emplean matrices de baja densidad (mayormente compuestas por `0's) y se hace necesario implementar un circuito que emule la multiplicación de matrices. La sección de chequeo de paridad puede ser formada con un Registro de Desplazamiento, Sumador, Acumulador Cíclico o CSRAA (siglas en inglés de Cyclic Shift-RegisterAdderAccumulator).

Los detalles de las implementaciones del bloque FEC pueden ser consultadas en 5.

Mapeo y Entrelazado

En el estándar, se definen 5 modos de mapeo: 64QAM, 32QAM, 16QAM, 4QAM and 4QAM-NR.

Los modos 4QAM y 4QAM-NR corresponden a la demanda de servicios móviles de alta velocidad, soportan transmisiones SDTV, a la vez que mantienen un balance adecuado entre cobertura y calidad de la señal en los receptores. Los modos de 32QAM y 64QAM corresponden a la demanda de altas velocidades y soportan HDTV y múltiples canales SDTV.

El mapeo de bits a símbolos se logra empleando memorias ROM donde se almacenan los símbolos correspondientes a cada mapeo (figura 4).

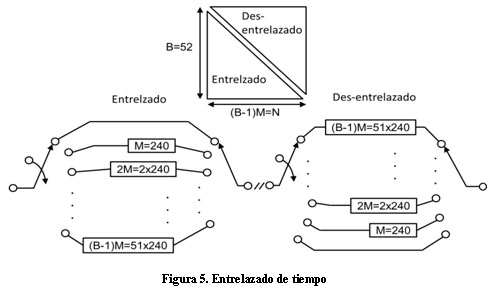

El entrelazado realizado en esta etapa es un entrelazado que ocurre en el dominio del tiempo. Este proceso previene que las palabras codificadas se vean afectadas por varios errores en caso de ráfagas, realizando una dispersión temporal 6. El entrelazado mejora el rendimiento de los sistemas de radio digital a expensas de aumentar el espacio en memoria, la complejidad del sistema y el retardo en el tiempo.

Como se puede observar en la figura 5, el bloque azul representa una división diagonal de BxN arreglos de símbolos en bloque conformando dos matrices triangulares. La primera mitad representa el Entrelazado y la segunda mitad el Des-entrelazado en el decodificador. Esta estructura se conoce como Entrelazado Convolucional (B, N) donde B es el número de ramas que tiene el Entrelazado y N es la profundidad del mismo; la rama cero se sincroniza con el primer símbolo de datos.

La norma establece dos modos de entrelazado:

· Modo 1: B=52 y N=240 símbolos.

· Modo2: B=52 y N=720 símbolos

La estructura del Entrelazado Convolucional (B, N) se implementa a base de bloques de memorias RAMs. La norma establece dos modos de Entrelazado, ambos con número de ramas igual a 52 pero de diferentes profundidades; para el modo 1 la profundidad es 240 y para el modo 2 la profundidad es 720. El entrelazado de mayor profundidad provoca mayor retardo de símbolos recibidos y el espacio total en memoria requerido es mayor, pero a su vez la eficiencia de corrección de error aleatorio aumenta.

Encabezado de Trama

Como parte de proceso de modulación, es necesario separar los símbolos OFDM (Multiplexación por División Ortogonal de Frecuencias) consecutivos rellenando la brecha resultante (intervalo de guarda). El Encabezado de Trama se emplea como intervalo de guarda temporal para proveer inmunidad a la dispersión de canal.

En el caso de DTMB la guarda consiste en secuencias pseudo-aleatorias conocidas, a las cuales no se les aplica modulación OFDM; este nuevo esquema de modulación se denomina TDS-OFDM (Time Domain Synchronous OFDM) porque es en estas secuencias pseudo-aleatorias donde se almacena la información necesaria para el sincronismo de la señal en el receptor. En otros sistemas de TDT como DVB-T 7 y ISDB-T 8, este intervalo de guarda se rellena con un prefijo cíclico de la IFFT empleada en la modulación OFDM. La nueva técnica posibilita una más rápida y eficiente sincronización, predicción de canal y ecualización.

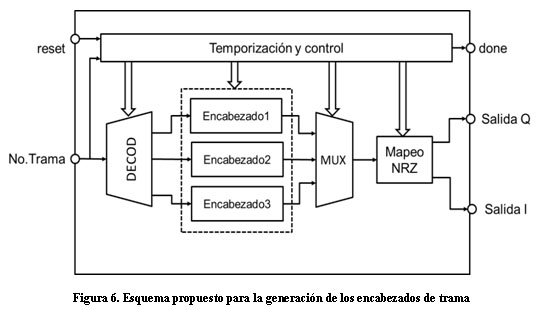

La implementación diseñada para este bloque debe satisfacer las 3 posibles variantes de Encabezado de Trama en la norma DTMB, como se ilustra en la figura 6 y la cantidad de símbolos varía entre 420, 595 y 945. Su elección depende principalmente de la geografía del entorno de transmisión, lo que determina la dispersión del canal correspondiente. En regiones con montañas se debe optar por valores mayores (Encabezado 3) que en las llanuras, aunque en este caso implica una disminución de la tasa de datos del 20%, según se ilustra en la fórmula 1.

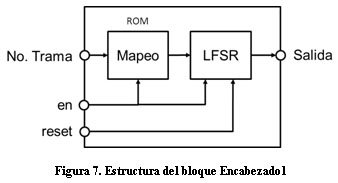

En el diseño se emplea un bloque decodificador que seleccionará cuál de los encabezados se va a generar según la selección del operador. Los encabezados consisten en secuencias pseudo-aleatorias binarias generadas a partir de LFSR.

En el caso de los encabezados 1 y 3, el LFSR es cargado con valores distintos según el orden de la Trama de Señal dentro de la estructura jerárquica superior, o Súper Trama (véase figura 2). Así, existirán 225 o 200 valores iniciales diferentes para el LSFR en los encabezados 1 y 3.

Un bloque de control se encarga de cargar en el LFSR los valores iniciales según el orden de la trama, leídos desde una memoria ROM como se muestra en la figura 7. En caso de transmitirse con el Encabezado 2, este será el mismo en cada Trama de Señal.

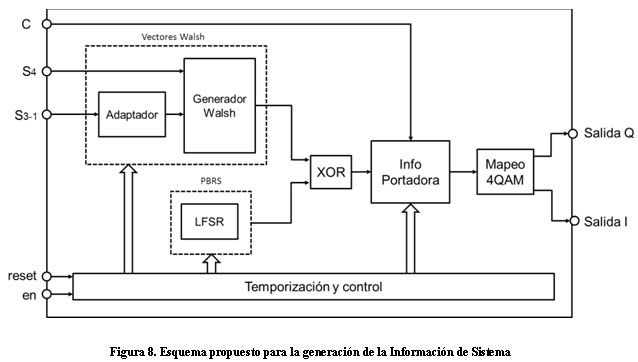

Información de Sistema

El bloque de Información de Sistema es el encargado de proveer la información necesaria referente a demodulación y decodificación, mapeo, tasas de codificación LDPC, modos de entrelazado, y modos de transmisión (multi-portadora o única-portadora).

En total existen 64 modos representados por 6 bits (s5s4s3s2s1s0 con s5 como el MSB) y la transmisión serealiza por técnicas de espectro esparcido, de forma que hay una adecuada protección contra el multitrayecto. El bit S5 realmente es reservado, y no es necesario considerarlo.

Los 6 bits de información son convertidos en 32 bits mediante técnicas de espectro esparcido, valiéndose de secuencias Walsh y Secuencias Pseudo-Aleatorias Binarias (PRBS), ambas de longitud 32. Después de esta conversión, a los 32 bits se le agregan otros 4 con información sobre el modo de transmisión (1 o 3780 subportadoras), conformando los 36 bits de Información de Sistema. Estos 36 bits se transforman en otros tantos símbolos luego de mapearlos 4QAM.

Los códigos Walsh se obtienen mediante la generación de una matriz cuadrada de orden 32, cada una de cuyas columnas identifica un vector según los valores de s3s2s1s0; las secuencias Walsh son comúnmente empleadas como secuencias de espectro esparcido.

En el diseño propuesto en la figura 8, el bloque Adaptador Walsh se encarga de proveer al generador de secuencias Walsh con la información sobre el orden del vector a generar. El bloque PRBS genera una secuencia aleatoria de 32 bits a partir de un LSFR de orden 5. El XOR entre estos 32 bits y los que se obtienen del generador Walsh constituyen los 32 bits menos significativos de la trama Información de Sistema. Anteponiéndole otros 4 bits con información sobre el modo de transmisión (multi-portadora o única-portadora) se obtienen los 36 bits, que posteriormente se mapean 4QAM.

Procesamiento del Cuerpo de Trama

El Cuerpo de Trama se forma al multiplexar los 36 símbolos de Información de Sistema con otros 3744 símbolos de datos., y está compuesto por C subportadoras, ocupando un ancho de banda de 5.67 Msps. C puede tomar 2 valores, C=1 o C=3780. El modo multiportadora será el analizado en este artículo, correspondiente a modulación OFDM con 3780 subportadoras.

El espaciamiento entre las subportadoras será:

Si se define ![]() como símbolo del Cuerpo de Trama y X(n) como la señal a la cual modular, la representación de la señal luego del proceso de modulación con C=3780 es:

como símbolo del Cuerpo de Trama y X(n) como la señal a la cual modular, la representación de la señal luego del proceso de modulación con C=3780 es:

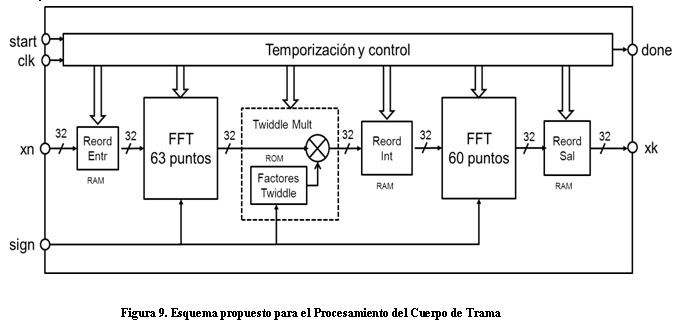

La similitud matemática entre (3) y la Transforma Inversa Discreta de Fourier (IDFT) conllevan que las implementaciones prácticas de un modulador OFDM pasen por implementaciones eficientes de IDFT, específicamente transformadas inversas rápidas de Fourier (IFFT).

Para esta aplicación, diseñamos una transformada de Fourier de 3780 puntos mediante la descomposición por Cooley-Tukey en otras dos de 63 y 60 puntos (3780 = 63 * 60), como se ilustra en la figura 9. Cada una de estas transformadas, a su vez fue calculada sobre la base de los algoritmos de Winograd 9 y empleando el reordenamiento propuesto originalmente por Good y

Thomas, para descomponerlas en transformadas más pequeñas. El proceso de diseño de este módulo escapa del alcance de este artículo y no será descrito.

Procesamiento en Banda Base

El procesamiento realizado a la señal en banda base luego de la IFFT se resume en un filtraje raíz cuadrada coseno alzado (SRRC, Square Root Raised Cosine por sus siglas en inglés).

El filtro está descrito mediante la ecuación 4:

Donde,

![]() Coeficiente roll off del filtro SRRC.

Coeficiente roll off del filtro SRRC.

![]() Ts es el período de símbolo.

Ts es el período de símbolo.

El diseño se auxilió de la herramienta fvtool de MATLAB, para la obtención de los coeficientes del filtro, y del Core Generator Fir Compiler de Xilinx para su implementación.

El diseño se basa en un filtro FIR, con característica simétrica de su respuesta, por lo que se reduce el número de recursos para su implementación. Aun así, el número de multiplicadores a emplear es la principal limitante. Estamos concibiendo el diseño para un FPGA de la familia Virtex-5 con bloques DSP48E formados por multiplicadores de 25x18 bits por lo que, a fin de emplear la menor cantidad de multiplicadores, se limitan los coeficientes de filtro y la señal a filtrar a una representación de 25 bits y a 18 bits respectivamente.

El orden del filtro a emplear está limitado por el número de multiplicadores a emplear, teniendo en cuenta que necesitamos 2 filtros idénticos para los canales I y Q. El FIR Compiler da la posibilidad de configurar el módulo para dos canales. Para un filtro

de orden 62, con un reloj de sistema 4 veces más rápido que la velocidad de las muestras (con lo cual se aumenta el nivel de paralelismo de los recursos empleados), se necesitan 17 bloques DSP48E, un valor que nos parece una utilización aceptable.

En la figura 10 se muestra la respuesta para de nuestra propuesta de filtro de orden 62, con el cual se logra una atenuación de casi 30dB en el mayor lóbulo fuera de la banda de paso.

CONCLUSIONES

El presente artículo describe el trabajo en un proyecto aun en desarrollo. Todos los módulos han sido diseñados y comprobados mediante simulaciones pero aun se trabaja en la integración de todos ellos y su implementación física.

Los bloques abarcados en este artículo han sido diseñados valiéndose en parte del System Generator y en parte mediante lenguaje de descripción de hardware VHDL, sintetizados con la herramienta XST de Xilinx ISE versión 12.1 para un FPGA xc5vfx70t-ffg1136, simulados empleando ModelSim y verificados además con herramientas de MATLAB.

La síntesis del diseño se ha realizado por etapas, para diferentes bloques por independiente. El elevado número de recursos de memoria, en especial la requerida para el entrelazado temporal y el procesamiento del bloque LDPC hacen imposible la implementación de todo el conjunto de módulos en el xc5vfx70t sin el empleo de memorias RAM externas al FPGA, fase contemplada en el futuro desarrollo del proyecto.

Hasta el momento el principal aporte del trabajo realizado, aun sin concretar en un modulador comercial, se basa en la obtención de bloques independientes plenamente funcionales, que constituyen un paso importante en la obtención de la verdadera independencia tecnológica en esta área.

Más allá de los costos de fabricación de un modulador comercial en el futuro, las implicaciones económicas más inmediatas del proyecto pasan por la venta de estos módulos de propiedad intelectual. Como referencia se puede tomar una oferta realizada a LACETEL por la compañía canadiense Axcera, fabricante de moduladores de TDT, que comercializa el software de configuración del FPGA para la norma DTMB por un valor de 1100USD.

Validación de resultados

La principal herramienta fue para la validación de resultados fue la réplica de las funciones implementadas con el System Generator en MATLAB, el cual también se empleó para la puesta a punto de los diseños de conjunto con ModelSim.

En la figura 11 se muestra el esquema en System Generator con la interconexión de los módulos Información de Sistema, Encabezado de Trama, Procesamiento de Cuerpo de Trama y filtro SRRC. Como se mencionó antes, dado el estado actual del desarrollo, aun no se han interconectado todos los bloques. En este modelo, se ha partió de la generación de números aleatorios para simular la aleatorización y codificación (FEC).

Para el esquema de la figura 11 se configura una modulación con el encabezado 2 (595 símbolos), en modo multiportadora (C=3780), mapeo 4QAM, LDPC modo 1 (razón 0.4) y entrelazado modo 2 (720 símbolos).

El bloque se control se manejar todo el proceso, incluyendo, además de los módulos antes descritos, la multiplexación, primero de los datos con la información de sistema para formar el cuerpo de trama, y luego de este con el encabezado.

Por otra parte, para la comprobación del bloque de mapeo y entrelazado se empleó el esquema mostrado en la figura 12, mientras que el esquema mostrado en las figura 13 sirvió para validar el diseño del bloque FEC. En la figura 12 se ilustra el esquema empleado para obtener una respuesta confiable (juegos de valores de prueba) con la cual se comprobaron las etapas de mapeo y entrelazado del diseño propuesto.

Además, fue de gran ayuda los anexos D y G del estándar DTMB, mediante los cuales se comprobó funcionalmente los bloques Información de Sistema y Encabezado de Trama, con los juegos de parámetros brindados.

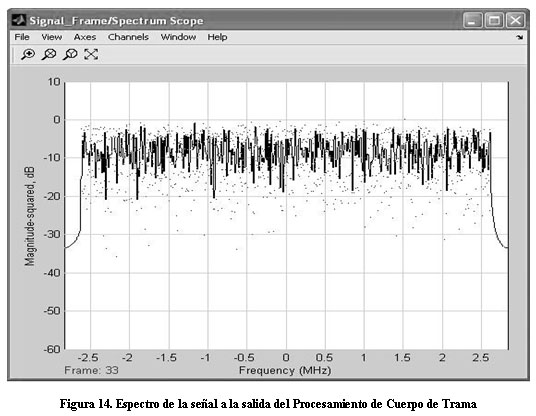

Mediante simulaciones, y empleando las herramientas de MATLAB, se comprueba la obtención de una señal de 6MHz de ancho de banda, de acuerdo a los requerimientos de modulación para el estándar DTMB. En la figura 14 se muestra el espectro de la señal en banda base modulada con 3780 subportadoras, para un ancho de canal de 6 MHz. Nótese que el ancho de banda es cercano al valor esperado de 5.67 MHz

REFERENCIAS

1. «Informe final de la sub-comisión técnica de la TV digital». Cuba, 2009

2. Estándar DTMB «Framing Structure, Channel Coding and Modulation for Digital Television Terrestrial Broadcasting System», GB20600-2006, Ago. 2006.

3. YANG ZHIXING: Conferencia «Technologies, Performance, Intellectual Property, and Applications of Chinese DTTB standard». Cuba, Dic 2007.

4. CHAO ZHANG, XIAO-LIN ZHANG, CHENG LU, ZHAN ZHANG:«The Technical Analysis on the China National Standard for Digital Terrestrial TV Broadcasting». School of Electronic Engineering, Beihang University, Beijing, China.

5. REY DOMINGUEZ, ADDIS Y RAYMOND RODRÍGUEZ, LUIS GIRALDO: «Diseño del Aleatorizador, la Codificación de Canal, Mapeo y Entrelazado de un modulador DTMB». Cuba, 2011.

6. SIERRA ROMERO, ALBERTO: «Diseño de la Codificación de Canal y Mapeo correspondientes a un modulador DVB-T», Cuba, 2010.

7. «Digital Video Broadcasting (DVB); Framing Structure, Channel Coding and Modulation for Digital Terrestrial Television,» ETSI, Tech. Rep. EN 300 744 v1.6.1, Ene. 1997.

8. «Transmission system for digital terrestrial television broadcasting» ARIB STD-B31 Version 1.6, Nov, 2005.

9. S. WINOGRAD: «On Computing the Discrete Fourier Transform». Mathematics of Computation, volume 32, number 141, Enero, 1978.

Recibido: Marzo 2012

Aprobado: Mayo 2012