Mi SciELO

Servicios Personalizados

Revista

Articulo

Indicadores

-

Citado por SciELO

Citado por SciELO

Links relacionados

-

Similares en

SciELO

Similares en

SciELO

Compartir

Ingeniería Electrónica, Automática y Comunicaciones

versión On-line ISSN 1815-5928

EAC vol.34 no.1 La Habana ene.-abr. 2013

ARTICULO ORIGINAL

Hardware reconfigurable para la reconstrucción de videos transmitidos por un mazo de fibras incoherente

Reconfigurable hardware for reconstruction of transmitted videos using Incoherent Optical Fiber Bundles

MSc. Pablo Montejo Valdés1, Alfredo Gardel Vicente2, Jorge García García2, Pedro R. Fernández Barbosa2, Jose Luis Lázaro Galilea2, Dr. Victor Escartín Fernández1

1 Centro de Investigaciones de Microelectrónica (CIME), Instituto Superior Politécnico ¨José Antonio Echeverría¨, Cujae, La Habana, Cuba. pablo.montejo@electrica.cujae.edu.cu , victor.escartin@electrica.cujae.edu.cu

2 Departamento de Electrónica, Universidad de Alcalá, España. alfredo@depeca.uah.es , jorge.garcia@depeca.uah.es , lazaro@depeca.uah.es

RESUMEN

La transmisión de imágenes mediante mazos de fibras ópticas no coherentes (IOFB) necesita información sobre la posición de cada fibra para ser usada en la reconstrucción de la imagen original. Otro importante requerimiento es poseer suficiente memoria para almacenar la imagen durante su reconstrucción y durante su retransmisión. La mayoría de las veces estos aspectos obligan el uso de memoria externa si se utilizan FPGAs en el sistema. Este trabajo presenta una solución a este problema. Se propone un sistema en un chip capaz de almacenar la información necesaria y las imágenes sobre las que se está trabajando usando un FPGA de bajo costo. Se presentan dos soluciones y se implementa la que resulta más ventajosa. Los resultados son discutidos. El uso de este método hace posible transmitir video usando IOFB y reconstruir las imágenes originales casi en tiempo real, debido a su baja latencia. Esta propuesta podría utilizarse en sistemas autónomos sacando ventaja de su nivel de compactación, fiabilidad y bajo costo.

Palabras claves: fibra óptica no coherente (IOFB), FPGA, sensor de imagen, transmisión de video.

ABSTRACT

Image transmission using incoherent optical fiber bundles (IOFB) requires calibration information used for reordering the fiber positions and reconstructing the original image. Another important demand consists in enough memory to store image during reconstruction and during retransmission. Most of the time, these aspects require to use external memory when FPGAs are used. This paper presents a solution in order of resolve this problem. A system on chip is proposed capable of to store needed information and images using a low cost FPGA. Two solutions are presented, the best is implemented. Results are showed. The use of this method makes possible to transmit video using IOFB and reconstruct originals images almost in real time because of its low latency. This proposal could be used in autonomous systems taking advantage of its compaction level, reliability and low costs.

Key words: Incoherent Optical Fiber Bundles (IOFB), FPGA, image sensor, video transmission.

INTRODUCCION

La transmisión de imágenes mediante mazos de fibra óptica coherente en ambientes donde el equipamiento electrónico resulta inutilizable o en extremo peligroso es frecuente en la actualidad. Endoscopios médicos, periscopios y otros aparatos han sido patentados para lograr estos fines en reactores nucleares, dentro del cuerpo humano y otros lugares con condiciones adversas para la transmisión de imágenes electrónicamente 1.

Menos frecuente resulta la utilización de mazos de fibra óptica no coherente para estos fines. El bajo precio de la propuesta ha atraído varios autores al tema años atrás 2-4. Sin embargo, el complejo mecanismo de reconstrucción de la imagen así como la cantidad de información a procesar ha mantenido estos algoritmos solo al alcance de los ordenadores.

El uso de FPGAs para acelerar el procesamiento de imágenes no resulta nuevo5. Incluso son empleados para acelerar algoritmos en procesamientos llevados a cabo desde ordenadores6. El propósito de este trabajo es extender el campo de acción de los mismos en la reconstrucción en tiempo prácticamente real de videos transmitidos por mazos de fibra óptica no coherente.

Este trabajo tiene como antecedentes múltiples investigaciones llevadas a cabo por el departamento de electrónica (DEPECA) de la Universidad de Alcalá7-10. Especialmente se debe destacar la Tesis doctoral «Modelado de sistemas de transmisión y reconstrucción de imágenes basados en mazos de fibra óptica no coherentes, en Departamento de Electrónica» 11.

Implementación

El sistema a desarrollar se explica partiendo del esquema mostrado en la Figura 1. Una taza proyecta su imagen en uno de los terminales de un mazo de fibras ópticas. Si se tratara de un mazo coherente, en el otro extremo se obtendría la imagen de la taza, pero cómo este es incoherente el resultado parece ser un conjunto de puntos sin sentido. Mediante un transductor óptico-electrónico se captan estos datos y se envían al FPGA. El monitor «1» muestra la escena que está captando la cámara. Utilizando la información de calibración de este mazo en específico, previamente obtenida y almacenada en su interior, el circuito lógico programable selecciona y organiza los píxeles de entrada para recuperar la información requerida de la imagen original. El monitor «2» muestra el video de salida del sistema.

Es de destacar algunos aspectos que resultan evidentes en la Figura 1 y no han sido aclarados hasta el momento:

· Los sistemas de acoplamiento óptico. Con el objetivo de simplificar el esquema, se omiten los dispositivos ópticos que resultan imprescindibles para el enfoque en la obtención de la imagen original y el acoplamiento entre el transductor óptico-electrónico y el mazo de fibras.

· El uso de imágenes con escala de grises. Se reservó la extensión al uso de sistemas en colores para trabajos futuros.

· El ruido de «sal y pimienta» obtenido. Este se debe a los espacios entre fibras y a la ausencia de estas, defectos estos inherentes a la construcción del mazo. Se considera como un aspecto admisible por la aplicación final que utilice el sistema.

Problemática de alto consumo de memoria

El principal problema a vencer para poder enfrentar la reconstrucción de imágenes de video transmitidas mediante mazos de fibra óptica no coherentes por FPGAs es la relativa baja capacidad de memoria interna de estos.

Los transductores ópticos-electrónicos tradicionales envían la información de video como una secuencia de píxeles barridos de izquierda a derecha y de arriba abajo. El dispositivo lógico programable deberá seguir el mismo esquema a su salida, sin embargo pudiera darse el caso, en dependencia de la distribución de las fibras del mazo en particular con que se esté trabajando, que el último pixel en recibirse sea el del borde superior izquierdo, el primero que debe transmitirse. Esto explica que para comenzar a transmitir la secuencia de salida es necesario almacenar el cuadro completo con anterioridad.

Así mismo también se entiende que durante la transmisión no deberá comenzar a recibirse un nuevo cuadro ya que esta información distorsionaría la registrada para algunos píxeles del cuadro anterior. Este problema tiene singular importancia cuando se trata de procesar señal de video, donde los cuadros se suceden con regularidad.

Variantes valoradas

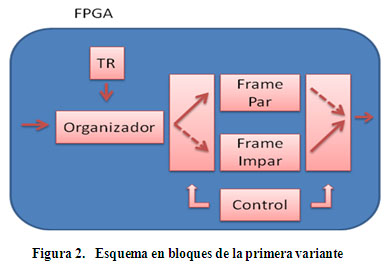

La Figura 2 presenta la primera variante de solución valorada. La idea que se implementa consiste en declarar dos zonas de memoria similares, con capacidad para alojar una imagen de salida completa cada una. De esta manera cada cuadro consecutivo se almacena en un bloque diferente: mientras se recibe y organiza uno en una zona de memoria, se transmite el anterior desde la otra zona.

El bloque Organizador es el encargado de, con la información de calibración del mazo disponible en TR, ir asignándole a los píxeles que van arribando su posición correcta en el cuadro de salida que corresponda, Frame Par o Frame Impar. Control selecciona cual de los bloques Frame está recibiendo datos desde Organizador y cual está enviando información a la salida.

Esta variante funciona perfectamente, pero tiene el inconveniente del alto gasto de recursos del FPGA. Se probó con imágenes de 252 x 252 píxeles no consiguiéndose su implementación en la serie de integrados de bajo costo Spartan de Xilinx por lo que hubo que recurrir a la familia Virtex del mismo fabricante, de mayores prestaciones.

La segunda variante reduce casi a la mitad los recursos empleados en la anteriormente explicada. La idea se puede definir como establecer una nueva secuencia de imágenes conformando cada una con píxeles de cuadros consecutivos.

En la práctica esto no es más que transmitir los cuadros a la salida permitiendo que los nuevos píxeles que arriben cambien parte de su información. Como resultado, una imagen transmitida contendrá información de dos cuadros consecutivos. Se rompe con la correspondencia tradicional donde cada imagen de entrada se corresponde con una de salida, en este caso un cuadro de salida se compone a partir de partes del último que se recibió completo y el que se está recibiendo en el momento en cuestión.

Este procedimiento trae consigo que aparezcan distorsiones en las zonas del video que presenten movimiento. Si bien para algunas aplicaciones esto no será un problema a considerar, esta dificultad puede minimizarse hasta su desaparición utilizando una propiedad típica de estos sistemas de reconstrucción de imágenes procedentes de mazos de fibra óptica no coherente: la imagen que se recibe posee mucha mayor resolución que su equivalente de salida11. Así, al ser mucho menor la cantidad de píxeles que se deben transmitir que los que se reciben, es posible, utilizando el mismo reloj del sistema, transmitir varios cuadros en el mismo tiempo que se reconstruye tan solo uno. Este procedimiento minimiza las variaciones entre imágenes consecutivas y disminuye sustancialmente las distorsiones en el video obtenido.

El esquema en bloques de esta variante se muestra en la Figura 3. Control Recepción organiza en Memoria el cuadro que está arribando, para ello, sobre escribe los datos de la imagen anterior conformando la nueva. Al mismo tiempo y en repetidas ocasiones, el bloque Control Transmisión recorre toda la memoria procesando nuevos cuadros conformados con partes de ambas imágenes.

Descripción de la implementación

Para la implementación del sistema se utilizó el System Generator 12.3 de Xilinx sobre Matlab 7.10.0.499 (R2010a) ( Figura 4).

ImagenSerieIn recibe la información de los píxeles «desorganizados», mientras ImagenSerieOut transmite el video ya organizado. PrimerPixel1 se utiliza para marcar el primer pixel de los cuadros de entrada y PrimerPixel indica su equivalente en los de salida.

La Figura 5 muestra la implementación del bloque Procesa Imagen. Básicamente posee tres partes fundamentales, el bloque de Recepción, el de Transmisión y una memoria Dual Port RAM.

Dual Port RAM

Esta memoria debe tener capacidad suficiente para almacenar un cuadro del video de salida completo. Mientras el circuito Recepción posee capacidad para escribir en cualquiera de sus localizaciones de memoria, Transmisión puede leerlas, cada uno de forma indistinta sin más arbitraje que el que realiza la propia RAM.

Bloque Recepción y Tabla de Reconstrucción

Los aportes en el ahorro de recursos de este bloque son los que hacen posible la posterior implementación en un FPGA de bajo coste. Es el encargado de recibir la secuencia de pixeles «desorganizada» proveniente de la cámara y con la información guardada en la TR ir reconstruyendo la imagen inicial al guardarlos adecuadamente en la memoria Dual Port RAM.

La TR almacena, utilizando para ello un único campo, la dirección absoluta de los píxeles de entrada que poseen información útil para la reconstrucción. La localización absoluta de estos en la imagen final se guarda utilizando 2 campos que se corresponden con las coordenadas (x;y). Por último se dedica un campo para un factor de corrección que permite eliminar o minimizar las diferencias existentes entre cada fibra del mazo (principalmente derivadas de que no todas las fibras atenúan la luz que transmiten en igual medida)11.

Esta forma de organización resulta ineficiente para el almacenamiento y uso de la TR dentro de un FPGA. Basado en esto se propone compactar la TR en tres campos:

Index_In: Guarda las direcciones relativas de los píxeles de entrada que poseen información válida. En lugar de guardar la dirección absoluta, resulta en menor espacio de almacenamiento si se guarda la diferencia existente entre la dirección de un pixel útil y el que le sigue.

Index_Out: Guarda la dirección absoluta en la imagen final donde debe guardarse el pixel.

Alfa: Indica el factor de corrección por el cual debe multiplicarse el valor del pixel en cuestión con el objetivo de corregir variaciones en el grado de atenuación de cada fibra en particular.

Como muestra la Figura 6, una máquina de estado es la encargada de controlar la generación de las direcciones para barrer la TR de forma que la información propia del pixel que llega al sistema sea la que se encuentre disponible. Adicionalmente genera la orden de escritura para Dual Port RAM.

El bloque Direciona_TR3 barre las direcciones de la TR hasta que no quedan por llegar pixeles del cuadro que se está recepcionando que contengan información de la imagen de salida. La entrada «en» incrementa la dirección de salida mientras que «rst» lleva a condiciones iniciales al comienzo de un nuevo cuadro.

Indica_n_pixels2 es el bloque encargado de indicarle a la máquina de estado si el pixel actual está registrado en la TR como un pixel útil o no.

Bloque Transmisión

Este bloque se caracteriza por su simplicidad ( Figura 7). Dado que esta variante propone independizar la velocidad de fotogramas a la entrada del sistema de la de la salida, entonces el resultado se reduce a barrer todos los píxeles de cada cuadro de forma continua. Se agrega una señal Ind_Imagen_Out para permitir sincronizar con el comienzo de cada cuadro.

RESULTADOS

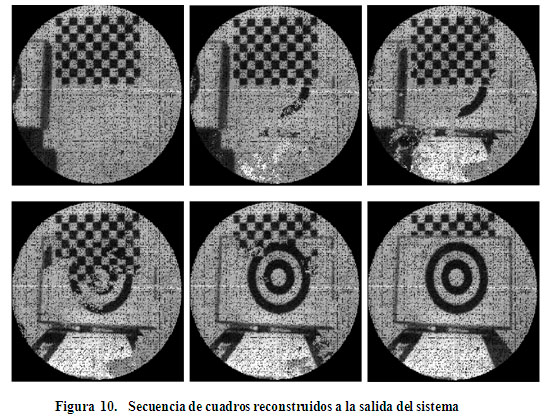

La Figura 8 muestra dos cuadros no consecutivos de un video (una diana se desplaza de izquierda a derecha). Tomando los cuadros anteriores al mostrado en la Figura 8 (izquierda) y los posteriores al mostrado en la Figura 8 (derecha) se conformó una señal de video que simula una transición abrupta de una escena a otra, como ejemplo de movimiento en extremo rápido.

La reproducción del nuevo video fue captada por un sistema como el descrito en este artículo (Figura 1). Uno de los cuadros entregados por la cámara de video se puede apreciar en la Figura 9.

El video de salida obtenido alcanzó 33 cuadros por cada cuadro de entrada. A manera de muestra en la Figura 10 se puede observar una selección de 6 cuadros equidistantes de los 33 cuadros que se corresponden con la transición desde la Figura 8 (izquierda) a la Figura 8 (derecha). Se puede apreciar claramente cómo aparece una transición aparentemente aleatoria de una escena a la otra. La reproducción de este video a la nueva velocidad de fotograma produce los mismos efectos visuales que el video del que se partió originalmente.

El sistema fue probado a partir de un banco de imágenes inyectado en un kit FPGA. En principio, esto permite considerar el trabajo válido para cualquier sistema con independencia de la fuente de imagen utilizada.

Para la implementación se utilizaron resoluciones de 1024 x 1024 en el video de entrada y de 252 x 252 en el reconstruido. Esta diferencia permite que mientras un cuadro de entrada demora 31,5ms en procesarse, los cuadros de salida se obtienen cada 0,952ms.

Se trabajó con 8 bits/pixel, 4 bits para el factor de corrección (2 bits enteros y 2 bits fracción) y 18 bits para el direccionado de los píxeles útiles.

Como hardware reconfigurable se ha seleccionado la FPGA XC6SLX150 de la familia Spartan 6 de Xilinx. En la Tabla 1 se muestran algunos de los resultados alcanzados según los reportes brindados por la compilación del proyecto en la herramienta ISE Design Suite 12.3 de Xilinx, pudiendo llegar a utilizar una señal de reloj de frecuencia igual a 66 MHz.

El hecho de procesar cada pixel del video de entrada en 2 pulsos de la señal de reloj, posibilita que con una señal de 15ns de periodo se puedan procesar 31f/s. Para las condiciones hasta aquí descritas la frecuencia de salida fue de 1050 cuadros/s.

Si definimos la latencia del sistema como el tiempo desde que entró un cuadro completo hasta que toda su información se procesó y transmitió, sería con las condiciones hasta aquí descritas de 31,5ms.

CONCLUSIONES

Se conformaron los cuadros del video de salida a partir de la información de cuadros consecutivos. Esta técnica permitió reducir casi al 50% el hardware empleado en el sistema.

El trabajo realizado en función de compactar la TR, manteniendo su información accesible de forma simple e inmediata, permitió minimizar la cantidad de memoria requerida para su almacenamiento. Esto evitó tener que recurrir a memoria externa en un dispositivo de hardware reconfigurable, logrando incluso la utilización de familias de bajo coste como la Spartan 6 de Xilinx.

El hecho de implementar este algoritmo en hardware reconfigurable abre la perspectiva de su uso en sistemas autónomos, pudiendo formar parte de un sistema de visión y/o monitoreo prácticamente en tiempo real debido a su latencia en extremo reducida.

AGRADECIMIENTOS

Este trabajo ha sido realizado en parte gracias al proyecto ESPIRA (REF-DPI2009-10143) financiado por el Ministerio de Ciencia e Innovación de España.

REFERENCIAS

1. Dujon, G., A. Parker, and A. Thomas: Visual image Transmission by fibre optic Cable, The secretary of State for Defence in her Britannic Majesty's Government of UK of GB and Northen Ireland, Patente No. US 5327514, 1994

2. Roberts, H.: Robust Incoherent Fiber Optic Bundle Decoder, Patente No. US 6587189 B1, 2003

3. Demuynck, O. and J.M. Menéndez: «Image Transmission through Incoherent Optical Fiber Bundle: Methods for Optimization and Image Quality Improvement» en WSEAS Transactions on signal processing, Vol 4. No. 9, 2008.

4. Dujon, G.F.: Calibration of incoherent optical fibre bundles for Image Transmission, en Dept. of Electrical Eng. and Electronics., University of Liverpool. UK. 1991.

5. Hiromoto, M., H. Sugano, and R. Miyamoto: «Partially Parallel Architecture for AdaBoost-Based Detection With Haar-Like Features» en Ieee Transactions on Circuits and Systems for Video Technology, Vol 19. No. 1, 2009.

6. Kalomiros, J.A. and J. Lygouras: «Design and evaluation of a hardware/software FPGA-based system for fast image processing» en Microprocessors and Microsystems, Vol 32. No. 2, 2008.

7. Fernández, P., et al.: Calibration of Incoherent Optical Fiber Bundles for Image Transmission. Fibers Detection, en IEEE International Symposium on Intelligent Signal Processing. WISP' 2007. 2007: Alcalá de Henares. Madrid. Spain.

8. Fernandez, P.R., et al.: «Location of Optical Fibers for the Calibration of Incoherent Optical Fiber Bundles for Image Transmission» en Ieee Transactions on Instrumentation and Measurement, Vol 58. No. 9, 2009.

9. Lazaro, J.L., et al.: «Sensor Calibration Based on Incoherent Optical Fiber Bundles (IOFB) Used For Remote Image Transmission» en Sensors, Vol 9. No. 10, 2009.

10. Fernandez, P.R., et al.: «A Focusing Method in the Calibration Process of Image Sensors Based on IOFBs» en Sensors, Vol 10. No. 1, 2010.

11. Fernández Barbosa, P.R.: Modelado de sistemas de transmisión y reconstrucción de imágenes basados en mazos de fibra óptica no coherentes, en Departamento de Electrónica. Universidad de Alcalá: Alcalá de Henares. 2011.

Recibido: Diciembre 2012

Aprobado: Enero 2013