Mi SciELO

Servicios Personalizados

Revista

Articulo

Indicadores

-

Citado por SciELO

Citado por SciELO

Links relacionados

-

Similares en

SciELO

Similares en

SciELO

Compartir

Ingeniería Electrónica, Automática y Comunicaciones

versión On-line ISSN 1815-5928

EAC vol.35 no.1 La Habana ene.-abr. 2014

ARTICULO ORIGINAL

Método de sincronización de planes en un controlador semafórico

Program synchronization method for a traffic controller

Ing. Alejandro Ruiz Villalonga1, Ing. Ernesto Alpizar Arteaga2

1. CITI, Instituto Superior Politécnico José Antonio Echeverría, Cujae, La Habana, Cuba, E-mail: aruiz@udio.cujae.edu.cu

2. Centro de Investigaciones de Microelectrónica (CIME), Facultad Ingeniería Eléctrica, Instituto Superior Politécnico José Antonio Echeverría, Cujae, La Habana, Cuba, E-mail: alpizar@electrica.cujae.edu.cu

RESUMEN

En el presente trabajo se presenta un método de sincronización de planes para un controlador semafórico, basado en aumentar la base de conteo de tiempo de las luces, el cual permitirá insertar la intersección nuevamente en la arteria sincronizada ante la aparición de algún desfasaje. El método implementado fue validado con la utilización de una tarjeta de control del controlador semafórico y se obtuvo como resultado que la sincronización de los planes se realiza en un máximo de tres ciclos. El controlador semafórico utiliza microcontroladores Microchip de gama media, se emplea para el desarrollo del firmware el compilador PIC C de CCS.

Palabras claves: controlador semafórico, plan, sincronización.

ABSTRACT

This paper presents a method of synchronizing traffic light controller plans, based on increasing time base count of lights, which will insert the intersection into synchronized artery again with the appearance of a mismatch. The implemented method was validated with the use of a controller card semaphoric control and was obtained as result that plans synchronization is performed in a maximum of three cycles. The traffic light controller uses Microchip mid-range family of microcontrollers so firmware development was used CCS PIC C compiler.

Key words: traffic controller, program, synchronization.

INTRODUCCION

El origen de este trabajo es la necesidad de lograr que un controlador semafórico pueda ser insertado en un sistema inteligente de transporte donde se garantice que las intersecciones que lo requieran estén sincronizadas entre sí. Esta sincronización garantiza la continuidad en el flujo de los vehículos a través de las intersecciones los cuales encontrarán el menor número de semáforos en roja posible [1]. Existen varios métodos para lograr esta sincronización entre intersecciones, uno de ellos es el utilizado en [2] para el cálculo de la distribución de tiempos de los semáforos conocido como método Webster [3][4].

Además de mantener la sincronización comentada, se requiere que el método implementado permita la optimización del algoritmo de trabajo con los contadores decádicos presentes en la intersección.

El funcionamiento del semáforo se basa en la ejecución de planes. Estos planes están formados por una serie de fases o combinaciones de luces las cuales tienen una duración determinada y se ejecutan en un horario establecido. Estas fases se agrupan en lo que se conoce como ciclos. De esta manera un plan está conformado de un ciclo el cual incluye a su vez una cantidad de fases. Este ciclo se repite de forma continua dentro del plan al cual pertenecen y a su vez el plan se ejecuta en una fecha y un horario predefinidos.

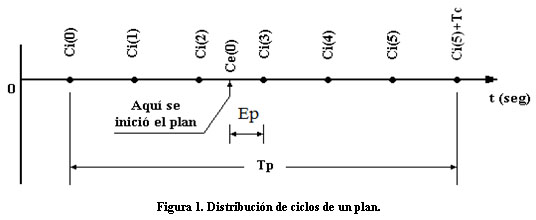

En la Figura 1 se muestra, a manera de ejemplo, la distribución en el tiempo de los momentos de inicios de los ciclos de un plan que toca ejecutar según la planificación y se han denotado como Ci(0), Ci(1), …

Cada uno de estos ciclos representa la secuencia de combinación de luces (fases) que se repiten a lo largo del plan. La duración del plan se denomina Tp y la de los ciclos Tc. En funcionamiento normal, todos los ciclos son iguales dentro del mismo plan en cuanto a su duración y a la secuencia de fases que contienen. Cada uno de los planes de una intersección, se encuentran almacenados en una memoria no volátil y contienen información de cuáles son las fases que están contenidas en sus ciclos, la duración de estas e información relacionada con la hora de comienzo del plan, así como su duración. Por tanto para saber qué plan hay que ejecutar en cada momento solo es necesario comprobar si la hora actual coincide con el intervalo de tiempo de alguno de los planes almacenados. Visto esto, en la Figura 1 se puede observar cómo se comenzó a ejecutar el primer ciclo del plan con un desfasaje (Ep). Este se define como la diferencia, en segundos, respecto al comienzo del ciclo Ci(3) que se había planificado. Si no se toma ninguna medida con este error, la intersección se desincroniza de las restantes en la arteria sincronizada.

Los motivos por los cuales se puede presentar este error son los siguientes

· Restablecimiento del servicio tras la pérdida del fluido eléctrico.

· Retorno al modo automático. Si el controlador estaba operando en modo manual, por ejemplo, al cambiar al modo automático realizará la búsqueda en la memoria, del plan a ejecutar.

· Tras la actualización de la fecha y la hora.

· Al finalizar un plan. El fin de un plan no tiene por qué coincidir con el fin de un ciclo, ya que al terminar el plan se debe esperar a que termine la última fase del ciclo en ejecución antes de buscar el nuevo plan en la memoria y garantizar así la continuidad de las fases. En esa espera aparece el error antes mencionado.

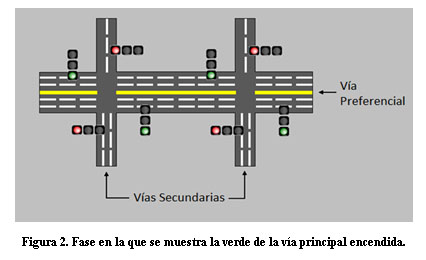

Una posible solución a este problema podría ser la utilizada en los controladores HT2000-B de procedencia china, en los cuales cuando se presenta esta situación se le aumenta la duración a las fases del ciclo que presenten una luz verde de vía preferencial encendida [5]. En la Figura 2 se muestra una fase de este tipo. Este aumento de la duración se realiza mientras exista un desfasaje Ep, y se normaliza la duración en el momento que se sincronice el semáforo.

Esta solución trae como consecuencia que los vehículos en las vías secundarias tengan que hacer una espera mayor. Además, aplicar este método al controlador semafórico desarrollado traería como consecuencia una incompatibilidad con la utilización de contadores decádicos regresivos en modo comunicación. En este modo, el controlador semafórico le envía a cada contador el número a mostrar así como el color correspondiente cada vez que termina su conteo. Para poder determinar qué número se debe mostrar cada vez, al inicio de la ejecución de cada plan hay que calcular las tablas de contadores. Estas tablas almacenan la duración de cada luz así como el identificador de la fase del ciclo en la cual corresponde enviar los datos a los contadores. Para el cálculo de estas tablas es importante que la duración de los ciclos siempre sea la misma en un mismo plan y por tanto, el método del controlador HT2000-B no cumple este requisito.

Una variante al método antes mencionado es sumarle tiempo a todas las fases del ciclo que presenten una luz verde encendida con independencia de la vía en cuestión. Esto aceleraría el proceso acortando el tiempo de sincronización hasta un valor de tres ciclos del plan como máximo. Esto aún no resuelve el problema con los contadores decádicos.

Otra forma de garantizar el sincronismo es el utilizado en [6] donde cada controlador de la arteria sincronizada tiene una entrada y una salida de sincronismo. Al recibirse un pulso de sincronismo en la entrada, este se replica a la salida la cual está conectada a su vez con la entrada de otro controlador mediante un cable. De esta manera se logran coordinar controladores en cascada. La desventaja de utilizar este método es el alto costo del cableado necesario para enviar el pulso.

El método que se propone consiste en modificar la base de conteo de tiempo de las duraciones de las fases en vez de la duración en sí de las fases. Esto significa que si en la operación normal del controlador semafórico se utiliza el segundo como unidad de conteo de tiempo, cuando se está en el proceso de corrección de los inicios de ciclos se utilizará 1.5 segundos como base. Con este cambio, una fase que tiene planificada duración de 10 segundos en realidad duraría 15 segundos. De esta forma se garantiza el alargamiento del tiempo del ciclo para corregir el desfasaje Ep. De la misma forma el número que representa la duración de cada una de las fases del ciclo se mantiene constante para cada plan y por tanto se pueden calcular las tablas de los contadores decádicos sin problemas.

El objetivo principal es por tanto, implementar un método de sincronización de planes que logre realizar esta acción en no más de tres ciclos y no interfiera con la operación de los contadores decádicos regresivos.

DESCRIPCIÓN DEL MÉTODO

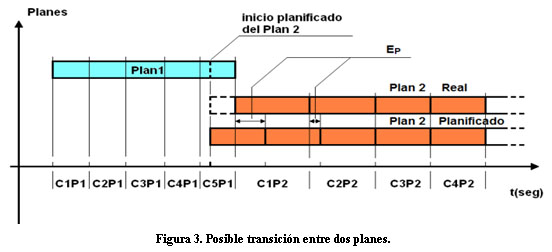

Como ya se comentó, el método de sincronización de planes que se propone consiste en la modificación de la base de conteo siempre que exista un desfasaje en esta sincronización. En la Figura 3 se puede observar una situación en la que está terminando la ejecución de un plan (Plan 1) y tiene que comenzar otro (Plan 2). Para la mejor comprensión de la situación, se ha puesto cómo sucedieron los ciclos del Plan 2 (Plan 2 Real) y debajo como deberían haber sucedido según la planificación (Plan 2 Planificado).

Como se observa, la terminación del Plan 1 no coincide con el inicio planificado para el Plan 2 de esta forma aparece un error de valor Ep. Este fenómeno se da debido a que no se puede terminar la ejecución de un plan a mediado de uno de sus ciclos ya que esto provocaría un posible cambio entre fases que no está contemplado en la ley vial y por tanto un posible accidente. Obsérvese como el primer ciclo del Plan 2 (C1P2) comenzó con un corrimiento del valor planificado. Sin embargo al agregar tiempo a la duración de este ciclo, en el siguiente (C2P2), el error Ep disminuye, y se elimina por completo en el ciclo C3P2.

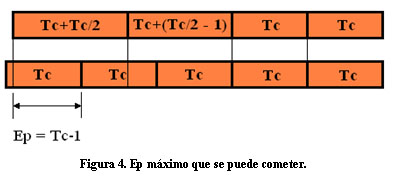

El error máximo Ep que puede ocurrir es de Tc - 1 segundos y representa el caso crítico. En cada ciclo, se puede agregar como máximo Tc/2 segundos y por tanto basta con dos ciclos para sincronizar el plan ya que en el primero se puede agregar Tc/2 y en el segundo Tc/2 1 lo cual equivale al error de Tc - 1 inicial. O sea, como máximo el plan estará sincronizado en dos ciclos (ver Figura 4).

IMPLEMENTACIÓN FIRMWARE

Para el desarrollo del firmware se utilizó el compilador PIC C de CCS (Custom Computer Services) y la plataforma protothreads como variante de sistema operativo. El mismo está dividido en nueve tareas que abarcan el funcionamiento del controlador semafórico. Además se utilizó la interrupción del módulo de comparación y captura en conjunto con el timer1 para lograr así una interrupción cada 10 ms y sirva de base para la temporización de las tareas del sistema operativo.

En la Figura 5 se muestra, de manera general, el diagrama de flujo de la sección del código correspondiente a la implementación del método propuesto.

La búsqueda del plan en la memoria, el cálculo de la duración del ciclo y el cálculo del error se realizan dentro de la función encargada de la actualización de los planes. Para el cálculo de la duración del ciclo basta con sumar las duraciones correspondientes a cada una de las fases que este contiene. Luego el error (Ep) se calcula como el resto de la división entre la diferencia de la hora actual en segundos (Hact) con la hora de inicio del plan en segundos (Hini) y la duración de ciclo (Tc). Este valor se resta de la duración de un ciclo del plan que se va a ejecutar. En las formulas (1) y (2) se muestra este cálculo.

El valor de Ep representa la cantidad de segundos que se deben adicionar dentro del ciclo para que los inicios de estos coincidan con los inicios de ciclos que habían sido planificados y la intersección quede sincronizada.

Este valor de error es multiplicado por dos para calcular la cantidad de conteos que se deben hacer con base de tiempo 1.5 segundos. Se hace esta multiplicación ya que cada conteo de este tipo sólo agrega 0.5 segundo al ciclo. Por ejemplo, si el error Ep que se obtiene es 20 segundos, entonces, hay que realizar 40 conteos de 1.5 segundos para agregarle a los ciclos la cantidad de 20 segundos.

Por cada conteo se decrementa una variable que al llegar a cero determinará que ya se ha sincronizado el plan y por tanto se debe volver a establecer los conteos de 1 segundo para el tiempo de los ciclos. La comprobación de esta variable se realiza en la interrupción del módulo de comparación y captura cada vez que pasa el tiempo correspondiente a un conteo de 1.5 segundos.

RESULTADOS

Para la validación del método desarrollado se realizaron dos experimentos. El primero consistió en configurar el controlador semafórico para que ejecute solo dos planes, a uno de ellos se le puso hora de comienzo a las 00:00:00, hora de fin 12:15:00 y duración de ciclo 48 segundos. Al segundo plan se le configuró hora de comienzo 12:15:00, hora de fin 23:59:59 y tiempo de ciclo 60 segundos, o sea que la transición debe ocurrir cuando termine un ciclo después de las 12:15:00. En la Figura 6 se observa una sección del resultado obtenido donde se muestra el momento de la transición (punto verde).

Cada punto azul representa la duración de un ciclo y el momento en que inició. Los puntos rojos representan la duración e inicio de cada fase contenida en los ciclos y el punto verde representa el momento donde se llevó a cabo el cambio de plan.

Véase como realmente la transición ocurrió un poco después de la hora 12:15:00, exactamente a las 12:15:12. Si se aplican las formulas (1) y (2) en este caso, se obtiene que:

![]()

Por tanto es necesario agregar 48 segundos que representan 48 x 2 = 96 conteos con base de tiempo 1.5 segundos.

La forma de determinar que realmente el plan se encuentra sincronizado, es tomar la hora de inicio de cualquiera de los ciclos que tengan la duración que se les ha planificado (60 segundos en el ejemplo, cualquiera de los últimos tres puntos azules), restarle la hora de inicio del plan y ver si el valor obtenido es un múltiplo de la duración del ciclo. Si lo es, entonces el plan esta sincronizado. En el ejemplo, tomemos el primer ciclo sincronizado, su hora de inicio es 12:18:00. Este valor se puede obtener como un número entero de ciclos (de 60 segundos) a partir de la hora de inicio del plan (12:15:00).

El segundo experimento tiene dos planes al igual que el anterior y el primer plan se le estableció la hora de comienzo a las 00:00:00, hora de fin 12:15:00 y duración de ciclo 48 segundos. Como el último ciclo del primer plan se termina a las 12:15:12 al segundo plan se le configuró hora de comienzo 12:15:12, hora de fin 23:59:59 y tiempo de ciclo 60 segundos. De esta forma el fin del último ciclo del primer plan coincide exactamente con la hora de inicio del siguiente plan. Así se presenta la situación en que no es necesario realizar el proceso de sincronización. En la Figura 7 se ve como no ocurre ninguna modificación en el tiempo de duración de los ciclos del segundo plan y este sería el mejor caso de una transición entre un plan y otro.

CONCLUSIONES

Una vez aplicado el método propuesto y analizados los resultados obtenidos de los experimentos desarrollados se puede decir que:

1. Se logra hacer que los planes de la intersección semafórica hagan coincidir los inicios de sus ciclos con los inicios de ciclos planificados.

2. Se requieren como máximo dos ciclos para lograr la sincronización del plan. Si el error Ep es inferior a la mitad de la duración del ciclo se requerirá solo uno para lograr esta sincronización.

3. Empleando esta forma en que se le agrega tiempo a los ciclos para implementar el método, se pueden calcular las tablas de los contadores decádicos regresivos sin hacer grandes cambios en el firmware ya implementado.

AGRADECIMIENTOS

Quisiéramos agradecer al Dr.C Alejandro J. Cabrera Sarmiento por la colaboración prestada en el desarrollo de este trabajo.

REFERENCIAS

1. DÍAS, M. «Métodos geométricos de coordinación de intersecciones reguladas por semáforos», XIV Congreso Internacional de Ingeniería Gráfica, Santander, España, 2002.

2. CARDOSO, E., MORENO V. «Análisis y diseño de software para la sincronización de intersecciones semafóricas». RIELAC, Vol.XXXIII 1/2012.

3. CALY MAYOR REYES SPÍNDOLA, R. «Ingeniería de Tránsito. Fundamentos y Aplicaciones. 7a.Edición, México D.F., México, 1994.

4. GONZÁLEZ CALLEROS, J. «Un modelo heurístico nuevo para el análisis del flujo vehicular». INAOE, Tonantzintla, Agosto 2003.

5. NATS.HT200B «Trafic signal controller, operation manual» . China, Enero 2005.

6. SUNYER, C.»Regulador semafórico especificaciones técnicas y funcionales». Barcelona, Mayo 2008.

Recibido: Noviembre 2013

Aprobado: Diciembre 2014