Mi SciELO

Servicios Personalizados

Articulo

Indicadores

-

Citado por SciELO

Citado por SciELO

Links relacionados

-

Similares en

SciELO

Similares en

SciELO

Compartir

Ingeniería Electrónica, Automática y Comunicaciones

versión On-line ISSN 1815-5928

EAC vol.35 no.1 La Habana ene.-abr. 2014

ARTICULO ORIGINAL

Arquitectura para transmisores HART de alta exactitud

Architecture for high accuracy HART transmitters

Ing. Deivid Efrain Tellez 1, MSc. Asfur Barandica López 2, Dr. Edgar Charry Rodríguez 3, Dr. Jorge Ramírez Beltrán 4

1. Empresa MEMS Ltda, São Paulo, Brasil. E-mail: deeftepo@usp.br

2. Universidad del Valle, Cali, Colombia, E-mail: asfur.barandica@correounivalle.edu.co

3. Universidade de São Paulo, Brasil, E-mail: charry@lsi.usp.br.

4. Instituto Superior Politécnico José Antonio Echeverría, Cujae, La Habana, Cuba. E-mail:jramirez@cih.cujae.edu.cu

RESUMEN

Los transmisores 4-20 mA de alta exactitud generalmente utilizan procesamiento digital de señales para compensar y calibrar su salida, debido a esto, el consumo de corriente está cerca del límite de los 4 mA. En este trabajo se presenta una arquitectura que permite adicionar la capacidad de comunicación digital HART y al mismo tiempo mantener los componentes y algoritmos usados en el transmisor original. Para el desarrollo de este trabajo se utilizó como base la arquitectura de un transmisor de presión piezoresistivo con un error de 0,2% de fondo de escala que usa un procesador digital de señales para sensores DSSP. Las pruebas demostraron que la arquitectura propuesta cumple con todos los requisitos del protocolo HART versión 6.0 y el error de la salida analógica y digital se conservó en el 0,2% de fondo de escala.

Palabras claves: transmisor de presión, HART, piezorresistor, exactitud.

ABSTRACT

In this paper a novel HART transmitter architecture is presented, based on a high accuracy 4-20 mA transmitter. Its main purpose is to develop a transmitter with a digital communication protocol without negatively affecting the 4-20 mA transmitter performance. It was used in this work a high accuracy pressure transmitter (error of less than 0.1% F.S.) that requires the use of digital signal processing for the compensation and calibration process. This circuit uses a digital sensor signal processor (DSSP) and the digital communication capacity in order to acquire the needed data to meet the HART standard requirements.

Key words: pressure transmitter, HART, piezoresistor, accuracy.

INTRODUCCION

La automatización de los procesos de producción se ha convertido en un requisito para la supervivencia de cualquier empresa en el sector industrial, es por esto, que se hace necesario el desarrollo de equipos de medición inteligentes y más exactos. Los protocolos digitales de comunicación industrial surgen como una respuesta a ésta necesidad, permitiendo además de la medición de la variable principal, configurar y leer otras informaciones del equipo como las unidades de ingeniería, otras variables de interés como la temperatura y si existe alguna falla. Teniendo en cuenta estas consideraciones, el objetivo de este trabajo es crear una arquitectura para un transmisor de presión HART a dos hilos con sensor piezoresistivo de alta exactitud. El protocolo HART adiciona la capacidad de comunicación digital a transmisores con señalización 4-20mA, siendo compatible con los sistemas de control tradicionales.

Son varios los problemas que deben ser resueltos y superados, el primero de ellos es el hecho que entre los sensores piezoresistivos se presentan diferencias en su sensibilidad y offset, adicionalmente, dichas características varían con la temperatura1. Es por esto, que se hace necesario el uso de procesos de calibración y compensación para garantizar un determinado nivel de error2. El segundo problema consiste en garantizar un consumo de corriente menor al impuesto por la señal 4-20mA y la modulación de la comunicación digital, y el último problema es garantizar una banda de error total (TEB) en la temperatura y en la presión menor a 0,2% de fondo de escala (FS).

En la literatura actualmente existen varias propuestas de arquitecturas para transmisores de presión con protocolos de comunicación digital: Jordana3 propone una basada en un micro controlador, en la que la resistencia del sensor se mide directamente por el tiempo de carga y descarga de un condensador, evitando así, los circuitos analógicos requeridos para la fuente de corriente usada en la excitación de los sensores piezoresistivos. Una arquitectura más compleja es presentada por Saponjic4, en la que se implementa un transmisor con protocolo de comunicación HART mediante un micro controlador y gran cantidad de componentes adicionales (transistores, amplificadores operacionales, etc.). Otra es basada en un microcontrolador y un ADC externo que se utiliza para compensar y calibrar sensores piezoresistivos5. Por último, Chuan6, presenta un transmisor basado en un procesador digital de la señal (DSP). La propuesta desarrollada en este trabajo se diferencia por usar un ASIC (Application Specific Integrated Crircuit) junto a un microcontrolador para garantizar una alta exactitud.

Presentación del problema

Actualmente existen varios tipos de sensores de presión piezoresistivos que hacen uso del silicio como el material de la membrana y tienen cuatro piezoresitores tipo P en una configuración de puente de Wheatstone7. En el proceso de fabricación de estos sensores se utilizan las mismas técnicas empleadas en la producción de circuitos integrados. Es por esto último que algunas características entre los diferentes lotes de producción pueden variar considerablemente y, en menor medida, entre los sensores de un mismo lote. El error en las mediciones puede ser catalogado según su origen en: errores estáticos (linealidad, histéresis), errores con la temperatura (variación del span y del offset) y errores de estabilidad de ruido (vibraciones mecánicas o ruido eléctrico)7.

Para corregir el error en la medición de la presión usando sensores piezoresistivos se han propuesto varios métodos de compensación y calibración (C&C) analógicos como los propuestos por Horn8, Gakkestad9 o Akbar10 y digitales, como los propuestos por Zatorre11 o la Maxim12. Siendo este último el que se ha seleccionado para este transmisor.

Sidney1 propone una arquitectura para un trasmisor con salida 4-20mA usando el procedimiento de C&C de la Maxim12, por lo que, su propuesta será usada como base en el desarrollo la arquitectura que se propone. Dicha arquitectura se basa en un ASIC, en el que es posible implementar todos los bloques que conforman el sistema, mediante el uso de algunos componentes externos para la fuente de excitación del sensor y el control de la corriente de lazo. El diagrama general de este transmisor es mostrado en la Figura 1.

Según lo reportado en la literatura, con esta arquitectura de transmisor se pueden lograr niveles de exactitud de 0,2%FS. Para mantener ese nivel de error, se debe utilizar dicho algoritmo de compensación y calibración12 en la arquitectura propuesta, de modo que, el ASIC debe conservarse. Por otra parte existen diferentes versiones del protocolo HART, la usada para el desarrollo de este trabajo fue la 6.0 que impone algunas restricciones al diseño, entre ellas que debe ser compatible con los sistemas tradicionales de señalización 4-20 mA y soportar la comunicación digital en ambos sentidos. En ésta versión de la norma se definen tres capas del modelo OSI (Open System Interconnection): la 1 , la 2 y la 7. La capa 1 (física) permite la presencia de las señales analógicas y digitales simultáneamente en el medio físico, usando señalización FSK (Frequency Shif-Keying) de fase continua, permitiendo una velocidad de 1200 bps. La señal analógica es la tradicional 4-20 mA con una frecuencia máxima de 25 Hz. La capa 2 (enlace de datos) es tipo maestro-esclavo y acepta hasta dos maestros simultáneamente en la red (uno primario y otro secundario). El algoritmo usado para el control de acceso al medio es el paso de testigo (Token Ring), con una secuencia de tiempos definidos que deben ser respetados. La última capa implementada en la norma HART es la 7 (aplicación), que es orientada a comandos y posee todos los procedimientos y tipos de datos definidos13.

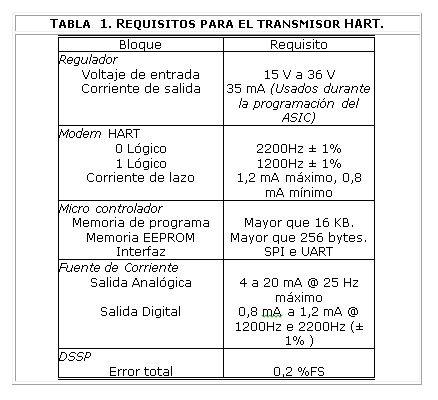

Entonces, para implementar el protocolo de comunicación HART es necesario: un microcontrolador, que dé respuesta a los comandos enviados por el maestro de la red; un módem Bell 202 para modular y demodular la señal digital, y los componentes para modular la señal digital en el lazo de corriente. La Tabla 1 resume las especificaciones de los componentes utilizados en el transmisor HART de alta precisión propuesto. El problema principal se resume en mantener los componentes utilizados en el transmisor 4-20 mA y agregar los nuevos al sistema, garantizando un consumo de corriente de lazo menor de 3,4 mA (ver Figura 2). Este es el límite impuesto por la necesidad de modular la señal digital HART con una amplitud de 600 uA sin saturación en el lazo de corriente.

Arquitectura Propuesta

La arquitectura propuesta se muestra en la Figura 3, donde el bloque «modem HART» representa toda la electrónica necesaria para el módem Bell 202. La propuesta mantiene los componentes del transmisor 4-20mA y son adicionados el procesador y el módem Bell 202. Para respetar los límites de corriente de lazo, se hace uso de una fuente de alimentación conmutada que realiza una conversión de potencia. Esto permite aumentar la cantidad de corriente disponible en el circuito de procesamiento de señales sin aumentar la corriente del lazo. A continuación se presenta una descripción de los bloques que componen el sistema.

Fuente conmutada

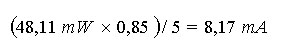

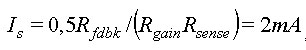

El objetivo principal de este bloque es asegurar una corriente Icc menor a 3,4 mA y al mismo tiempo proporcionar una corriente Ie superior a 4mA. Esto es posible mediante la realización de una conversión de potencia, para lo cual es necesario utilizar una fuente de alimentación conmutada. El LTC3642 es un convertidor Step-Down que regula la tensión de salida en 5 VDC, de acuerdo con las especificaciones del fabricante, tiene una eficiencia superior al 85% para corrientes de carga por encima de un miliamperio y tensión de entrada inferior a 15 V. En el peor de los casos, la potencia disponible será:![]() (donde

(donde ![]() es la tensión en la resistencia de lazo utilizada por el protocolo HART, típicamente 250

es la tensión en la resistencia de lazo utilizada por el protocolo HART, típicamente 250 ![]() ). Por lo tanto, se espera teóricamente una corriente Ie de

). Por lo tanto, se espera teóricamente una corriente Ie de  .

.

Este circuito integrado (CI) necesita de un filtro de salida LC, cuya finalidad es almacenar energía entre las conmutaciones de la fuente, lo que permite la regulación. El algoritmo de control utilizado en este chip es el siguiente: cuando la tensión es inferior a 4,968 V, el modo de ráfaga se habilita, en el cual, el transistor de carga permite la conducción de corriente desde el circuito de entrada para el filtro salida; esta corriente se mide y se compara con un valor de referencia ![]() (ajustable entre 25 mA y 115 mA). Cuando este valor se iguala, el transistor de carga pasa a corte y se pone en saturación el transistor de descarga, que permite el flujo de corriente por el filtro de salida. Cuando la corriente de descarga llega a cero, un nuevo ciclo comienza. Este procedimiento se repite hasta alcanzar una tensión de 5 V en la salida.

(ajustable entre 25 mA y 115 mA). Cuando este valor se iguala, el transistor de carga pasa a corte y se pone en saturación el transistor de descarga, que permite el flujo de corriente por el filtro de salida. Cuando la corriente de descarga llega a cero, un nuevo ciclo comienza. Este procedimiento se repite hasta alcanzar una tensión de 5 V en la salida.

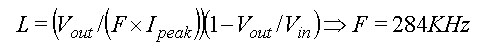

La corriente ![]() fue configurada en su valor mínimo (25mA) y se procedió a diseñar el filtro de salida, calculando los siguientes valores: la inductancia mínima es

fue configurada en su valor mínimo (25mA) y se procedió a diseñar el filtro de salida, calculando los siguientes valores: la inductancia mínima es ![]() con un

con un ![]() . Se utilizó un valor de inductancia de

. Se utilizó un valor de inductancia de ![]() , por su disponibilidad comercial. Utilizando éste resultado se calculó el valor mínimo del condensador de la siguiente manera:

, por su disponibilidad comercial. Utilizando éste resultado se calculó el valor mínimo del condensador de la siguiente manera:![]() con

con ![]() , un valor de

, un valor de ![]() fue utilizado por disponibilidad comercial. Finalmente, se espera que la frecuencia de conmutación sea de

fue utilizado por disponibilidad comercial. Finalmente, se espera que la frecuencia de conmutación sea de  .

.

Utilizando como base la propuesta de Sclocchi14 se empleó un filtro LC con amortiguación paralela en la entrada del LTC3642. Para asegurarse de que los componentes de alta frecuencia no afectaran a la señal analógica, se decidió utilizar una frecuencia de corte para el filtro diez veces menor que la frecuencia de funcionamiento de la fuente de alimentación conmutada, es decir, = 28,4 KHz. Por conveniencia, el valor de la inductancia de filtro de entrada es el mismo que el del filtro de salida (![]() ), por lo tanto,

), por lo tanto,![]() . La amortiguación de este filtro se consigue mediante la adición de un condensador en serie con una resistencia, en paralelo con el condensador de filtro LC de entrada. El valor del condensador es de 4 veces el valor de Cin (4,9 x 4 = 19,6 µF) y la resistencia es de

. La amortiguación de este filtro se consigue mediante la adición de un condensador en serie con una resistencia, en paralelo con el condensador de filtro LC de entrada. El valor del condensador es de 4 veces el valor de Cin (4,9 x 4 = 19,6 µF) y la resistencia es de ![]() . Este filtro tiene una baja impedancia (43

. Este filtro tiene una baja impedancia (43 ![]() ) en la frecuencia de funcionamiento del protocolo HART (1200 Hz y 2200 Hz), lo que constituye un problema, ya que ésta define la impedancia de entrada del transmisor y un valor bajo, en comparación con la resistencia de lazo (250

) en la frecuencia de funcionamiento del protocolo HART (1200 Hz y 2200 Hz), lo que constituye un problema, ya que ésta define la impedancia de entrada del transmisor y un valor bajo, en comparación con la resistencia de lazo (250 ![]() ), impediría la detección de la señal HART del transmisor. De modo que se añadió una resistencia de 300

), impediría la detección de la señal HART del transmisor. De modo que se añadió una resistencia de 300 ![]() en serie con la inductancia del filtro de entrada. Los subsistemas se muestran en la Figura 4.

en serie con la inductancia del filtro de entrada. Los subsistemas se muestran en la Figura 4.

Diseño del circuito conversor voltaje/corriente

El circuito utilizado en el transmisor se basa en el trabajo presentado por la Maxim15 (ver Figura 5). El principio de funcionamiento es el siguiente: el amplificador operacional está configurado en realimentación negativa, por tanto, ![]() y

y ![]() están a la misma tensión. Debido a que la corriente de salida del lazo es la suma de las corrientes a través de estas resistencias, deben ser utilizados valores de resistencia que garanticen que esa corriente sea aproximadamente igual a la corriente por

están a la misma tensión. Debido a que la corriente de salida del lazo es la suma de las corrientes a través de estas resistencias, deben ser utilizados valores de resistencia que garanticen que esa corriente sea aproximadamente igual a la corriente por ![]() , de forma tal, que la corriente de salida del lazo sea controlada cambiando el voltaje en

, de forma tal, que la corriente de salida del lazo sea controlada cambiando el voltaje en ![]() . Esto se realiza variando la corriente en la entrada no inversora del amplificador operacional, para lo cual son utilizadas las resistencias

. Esto se realiza variando la corriente en la entrada no inversora del amplificador operacional, para lo cual son utilizadas las resistencias ![]() y

y ![]() . Para permitir la operación de este circuito, tanto el transistor Q1 como el amplificador operacional deben trabajar en la zona lineal, para lo que es usada la resistencia

. Para permitir la operación de este circuito, tanto el transistor Q1 como el amplificador operacional deben trabajar en la zona lineal, para lo que es usada la resistencia ![]() .

.

Para calcular los valores de todas las resistencias primero se debe definir ![]() y

y ![]() , teniendo en consideración, que no debe saturarse Q1 es utilizado un valor de

, teniendo en consideración, que no debe saturarse Q1 es utilizado un valor de ![]() igual a 50

igual a 50 ![]() , asegurando una tensión de 1 V con una corriente Is de 20 mA. El valor de

, asegurando una tensión de 1 V con una corriente Is de 20 mA. El valor de ![]() fija entonces en 100 k

fija entonces en 100 k![]() , valor con el que la corriente a través de esta resistencia es de 10 µA cuando la corriente por el lazo es de 20mA.

, valor con el que la corriente a través de esta resistencia es de 10 µA cuando la corriente por el lazo es de 20mA.

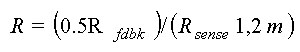

![]() tiene por objeto garantizar 16 mA de span en la salida analógica utilizando una señal de entrada entre 0,5 V y 4,5 V (Salidas estándar del ASIC). Por lo tanto, para una variación en la entrada de 4 V se debe obtener una salida de 16 mA, es decir

tiene por objeto garantizar 16 mA de span en la salida analógica utilizando una señal de entrada entre 0,5 V y 4,5 V (Salidas estándar del ASIC). Por lo tanto, para una variación en la entrada de 4 V se debe obtener una salida de 16 mA, es decir ![]() , que es igual a 500 k

, que es igual a 500 k![]() . Como la señal de entrada a cero presión es de 0,5 V, la corriente Is será de

. Como la señal de entrada a cero presión es de 0,5 V, la corriente Is será de  , entonces

, entonces ![]() se ajusta para adicionar los 2 mA faltantes asi:

se ajusta para adicionar los 2 mA faltantes asi: ![]() , asegurando 4 mA a presión cero.

, asegurando 4 mA a presión cero.

La resistencia Rx se usa para disipar potencia, pero se debe utilizar un valor que no sature el transistor cuando la salida sea de 20 mA, por tanto,![]() , es decir, menor de 700

, es decir, menor de 700 ![]() , el valor seleccionado fue de 390

, el valor seleccionado fue de 390 ![]() .

.

Circuitos adicionales para el Modem Bell 202

El módem Bell 202 utilizado fue el Maxim DS8500 que necesita de un filtro pasa banda con frecuencias de corte de 500 Hz y 10 KHz en la entrada. El circuito utilizado16 para este fin se compone de un filtro RC pasa bajo con una frecuencia de corte de 10 kHz y un filtro RC pasa alto con frecuencia de corte de 480 Hz. La señal de salida de este modem es de 500 mVp-p, por lo que, se debe calcular el valor de la resistencia de acople al conversor voltaje / corriente (V/I) para garantizar una salida de 1,2 mAp-p como lo indica la norma HART. Para no alterar el funcionamiento del conversor V/I esta señal de salida deberá ser desacoplada en DC. En el cálculo de esta resistencia se utiliza la siguiente ecuación  . El subsistema de bloques se muestra en la Figura 6.

. El subsistema de bloques se muestra en la Figura 6.

Algoritmo de Compensación y Calibración

El algoritmo de compensación y calibracion12, utiliza una matriz de tres presiones por tres temperaturas para el cálculo de los coeficientes de ajuste del sensor de presión y del convertidor voltaje-corriente. Este algoritmo se ha desarrollado para utilizarlo en el ASIC MAX1464 y hace uso de los diferentes recursos que tiene ese dispositivo Es importante precisar que para la medición de la temperatura se utiliza el sensor interno del MAX1464, por lo que el sensor de presión debe estar ubicado cerca él.

El proceso de compensación y de calibración (C&C) es el siguiente: inicialmente se debe programar el microcontrolador en modo sleep, pues el mismo bus SPI (Serial Peripheral Interface) usado por el micro controlador es utilizado para la comunicación digital con el MAX1464 durante la C&C. Posteriormente se debe controlar la temperatura del ambiente en el que se encuentra el transmisor por un tiempo de estabilización de dos horas. Después de esta espera se almacena el valor de salida del sensor de temperatura, presión (mínima, media y máxima), y los valores de la corriente de lazo en dos niveles de referencia del DAC (1/4 y 3/4 del rango total). El procedimiento anterior se repite para los otros dos puntos de temperatura, siempre respetando el tiempo de estabilización.

El algoritmo compensa y corrige inicialmente el sensor de temperatura, ya que su salida se utiliza como base para el cálculo de los valores de ajuste del sensor de presión. Se utilizó un polinomio de tercer orden para el ajuste del sensor de presión. Con una matriz compuesta de tres presiones en cada temperatura se generan los coeficientes que modelan el comportamiento del sensor de presión, utilizando polinomios de segundo orden. En este punto tenemos tres modelos diferentes para el sensor de presión, cada uno con 3 coeficientes. Entonces, un polinomio de tercer orden de los coeficientes en función de la temperatura es generado, y será utilizado finalmente para corregir el sensor de presión.

Con los datos obtenidos del convertidor V/I se modela el lazo de corriente del transmisor con un polinomio de segundo orden. El nivel de error obtenido usando este algoritmo es de 0,1% FS en la salida analógica y digital.

Firmware del transmisor

El código desarrollado para cumplir con el protocolo HART debe ser independiente entre las capas, de modo que se puedan reutilizar. Para lograr este objetivo, es necesario emplear los SAP (Service Access Point) definidos en la norma, y además garantizar que su ejecución siempre devuelva el control de ejecución al programa principal. Para facilitar éste desarrollo se utilizó un sistema operativo de tiempo real en el microcontrolador, el RTOS-PICC del compilador CSS. Una prueba de este sistema operativo confirmó que las tareas no se llevan a cabo sobre una base regular de tiempo, por lo que se debe tener cuidado en la codificación, evitando tiempos excesivos de ejecución. Entonces, algunas tareas sensibles al tiempo fueron implementadas utilizando interrupciones temporizadas, entre ellas, la medición de tiempos de bits utilizada por la capa MAC.

La arquitectura utilizada en el código es la siguiente: cada capa se implementa con una tarea periódica del sistema operativo (RTOS), la cual verifica el estado de las variables binarias (banderas) de su capa. Cada bandera indica una acción que debe ser realizada por la capa. Las acciones son ejecutadas por funciones que implementan los SAP definidas en la norma HART. Estas funciones son responsables de borrar la bandera después de la finalización de la acción y, si es el caso, cargar los resultados de la transformación efectuada en una posición de memoria previamente definida y activar las banderas necesarias para invocar la ejecución de otro SAP.

La capa física, además de la función periódica del RTOS, posee algunas funciones orientadas al evento, las cuales usan las interrupciones externas del microcontrolador y son responsables por las comunicaciones. La estrategia utilizada para administrar la memoria fue compartirla por todos los SAP, utilizando como parámetros los punteros a las direcciones, para evitar el uso innecesario de memoria RAM.

Firmware del MAX1464

El Max1464 es el encargado de realizar el procesamiento digital de la señal, para esto los coeficientes calculados en el procedimiento de C&C son programados para corregir el comportamiento del sensor. Adicionalmente, para dar soporte a los comandos HART que modifican la corriente del lazo, fue necesario programar un bloque «multiplexor» para poder fijar el valor usando comandos digitales. En la Figura 7 pueden observarse los bloques conceptuales del firmware. Finalmente un saturador es necesario para garantizar que la señal analógica de salida estará siempre entre los valores permitidos (4-20mA) sin importar las configuraciones usadas.

Resultados

A continuación se presentan los resultados de diferentes pruebas realizadas a los prototipos del transmisor de presión:

Regulador Conmutado

Inicialmente fue calculada la eficiencia de este circuito de forma aislada, usando diferentes tensiones de entrada (Vin) y resistencias de carga (Iload), ver Tabla 2. Con estos valores se pudo determinar que la corriente máxima que puede ser drenada por la electrónica (Ie de la Figura 5) es de 5.26 mA para un Vin de 12 VDC, para respetar la limitación de 3,4 mA de Icc. Para una tensión Vin de 15 VDC esa misma corriente Ie es de 6,32 mA. También fue observado que la eficiencia de este circuito disminuye para valores de tensión mayores a 15VDC, pero el circuito mantiene un valor de corriente de lazo más bajo que el umbral de 3,4 mA debido a la mayor potencia disponible en la entrada.

Consumo de Corriente del Transmisor

El propósito de estas pruebas fue medir el consumo total del transmisor a medida que se adicionaban los diferentes bloques que conforman el sistema. Estas mediciones fueron realizadas con una corriente Is igual a cero, permitiendo que la corriente de lazo fuera igual a Icc (ver Figura 5).

El primer bloque que se adicionó fue el ASIC (MAX1464) junto con los componentes adicionales que él necesita. La corriente medida fue de 2.015 mA para una tensión de alimentación de 12V. En las mismas condiciones el transmisor propuesto por Sidney1 consume 3,1 mA, por lo que, el uso de la fuente de alimentación conmutada representa una disminución en esta corriente de 1.1 mA. Esto se debe a que la propuesta de Sidney usa una como fuente un regulador linear y en este trabajo se usa una fuente conmutada. El siguiente paso fue agregar los componentes alimentados a 3,3 V (Microcontrolador PIC, módem HART y regulador lineal). Dado que el PIC tiene un consumo variable dependiendo del modo de operación en el que este configurado. Se fijó inicialmente en modo de suspensión (sleep), que es el menor consumo posible. En esta configuración la corriente consumida fue de 2,0185 mA y los voltajes de los reguladores de Vdd y Vdd3 fueron de 5,012 V y 3,327 V respectivamente.

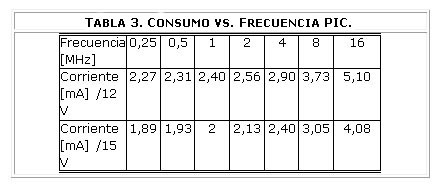

Para determinar la configuración que debe ser usada en el microcontrolador, fue medido el consumo total del sistema en las diferentes configuraciones. Los resultados de estas mediciones se presentan en la Tabla 3 y muestran que con el circuito alimentado a 15 V, como son los requisitos, la máxima frecuencia del oscilador interno del PIC es de 8 MHz, fijando una corriente Icc de 3,051 mA.

Modem Bell 202

Una vez verificado el cumplimiento de los requisitos de consumo, el siguiente paso fue comprobar los circuitos del módem HART: acople al bucle de corriente y filtro de entrada. Para esto, una señal sinusoidal de entre 286 Hz y 40 KHz se utilizó para simular la salida del DS8500. La señal de salida fue medida como la tensión en la resistencia del bucle (250 ![]() ). Los resultados presentados en la Figura 8 muestran que el circuito modula la corriente de lazo en el rango de frecuencias HART con una ganancia constante, disminuyendo a valores superiores a 10 KHz. La respuesta en frecuencia de los filtros de entrada se midió usando esa misma señal, ver Figura 8. El comportamiento fue el esperado, con una franja de paso de pista entre 500 Hz y 10 kHz y una ganancia cercana a uno en la banda de paso.

). Los resultados presentados en la Figura 8 muestran que el circuito modula la corriente de lazo en el rango de frecuencias HART con una ganancia constante, disminuyendo a valores superiores a 10 KHz. La respuesta en frecuencia de los filtros de entrada se midió usando esa misma señal, ver Figura 8. El comportamiento fue el esperado, con una franja de paso de pista entre 500 Hz y 10 kHz y una ganancia cercana a uno en la banda de paso.

Finalmente, la amplitud de la señal medida en la resistencia de lazo fue de 240 mVpp a 1213 Hz y 244 mVpp a 2192 Hz (0.976 mApp). Como la ganancia del filtro de entrada es cercana a uno, tenemos 240 mVpp en la entrada del módem, tensión más alta que la necesaria por el DS8500 (120 mVpp) para la demodulación sin errores. Por lo tanto, se puede decir que estos circuitos cumplen todos los requisitos para los filtros del módem HART.

Pruebas del Protocolo de Comunicación HART.

Para probar el código desarrollado en el micro controlador, se utilizó el software «HART server Basic Edition», disponible en la página web de la HCF (HART Communicaton Fundation), que es un servidor OPC (object linking and embedding for process control) para dispositivos HART. Este programa utiliza un puerto tipo COM del computador para comunicarse con el equipo HART, por lo que un módem USB / HART fue utilizado para este propósito. Con el software configurado y el módem en funcionamiento fueron probados los diferentes comandos del estándar utilizando un prototipo 100% funcional del transmisor.

En la Figura 9, se puede ver cómo los parámetros de identificación del equipo son correctamente leídos por el servidor, lo que indica una buena comunicación HART entre ellos. También se puedo observar el valor de la corriente del lazo y el porcentaje de la escala completa, lo que indica que el transmisor responde a los comandos de lectura de las variables dinámicas. Con las dos pruebas anteriores, se puede decir que el transmisor cumple con los comandos universales del protocolo HART.

Los comandos implementados y probados en el transmisor desarrollado son: 0, 1, 2, 3, 6, 7, 8, 9, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 34, 35, 38, 42, 44, 48, 50, 54. El comando que necesita más tiempo de procesamiento es el comando 35 (permite cambiar el rango de la salida analógica), porque debe calcular los coeficientes de ajuste y programar el MAX1464. Una medición del tiempo total de procesamiento del comando por la capa de aplicación resulto en un tiempo de 28,6 mseg, tiempo suficiente para generar y transmitir la respuesta. Finalmente, se verificó que todas las respuestas a los comandos son generados por el transmisor en un máximo de 150 mseg, tiempo inferior al límite (STO - Slave Time Out), de 256 mseg del protocolo HART.

Medición del error

Para medir el nivel de error del transmisor fueron compensados y calibrados 4 prototipos. Después de la calibración fueron expuestos a diferentes ciclos de temperatura y de presión. Las medidas de las salidas analógicas y digitales para cada valor de presión y temperatura fueron almacenadas, en la Figura 10 puede observarse el error para la salida analógica y digital del prototipo #4 a 50 grados.

Analizando esta figura se pudo observa que el error en la salida digital es menor que en la salida analógica, lo que es esperado, porque en esta salida participan menos componentes, disminuyendo las fuentes de error. Este comportamiento es constante en todas las mediciones, por ejemplo para el caso del prototipo #2 a 25 grados, el error en la salida analógica está entre +0,12%FS y +0.02%FS, y para la salida digital el error está entre +0,07%FS y +0,02%FS.

Se observó que conforme los sensores eran expuestos a más ciclos de presión y temperatura un desplazamiento del error aparecía. Un ejemplo de este comportamiento fue el transmisor #3 en el cual a 25°C en la rampa ascendente del primer ciclo de temperatura presentaba un error medio de -0,03494457 % FS. En la rampa descendente presentó un error de 0,01364049 % FS a 25°, en el siguiente ciclo los errores fueron de 0,05197292 % FS y 0,06504887 % FS. Este comportamiento se cree que es debido a pequeños cambios en los componentes físicos del transmisor de presión (sensores, resistencias y capacitores) debido a la temperatura. Para demostrar esta hipótesis fue realizado el procedimiento de compensación después de exponer los transmisores a repetidos ciclos de presión (20 en total) y a dos ciclos de temperatura. Los resultados mostraron un cambio en los valores medidos del sensor de presión. Como puede verse en los valores medidos para 25°C del transmisor #3 los cuales originalmente fueron de -19303, 5798 y 30099 (Lectura del ADC para presión mínima, media y máxima). Y que en la C&C posterior fueron de -19260, 5824 y 30111. Lo que representa un incremento máximo de 0,87% FS. Por tanto se recomienda realizar un procedimiento de envejecimiento de los transmisores antes de realizar la C&C, llevando los componentes a un estado más estable, evitando esos cambios durante la operación continua del sistema.

CONCLUSIONES

La utilización del procesamiento digital de señales para el desarrollo de transmisores de presión aumenta el grado de exactitud y precisión de estos sistemas, pero aumenta la cantidad de componentes necesarios y con ellos la corriente consumida por el circuito, en este trabajo fue presentada una arquitectura basada en fuentes conmutadas que permite solucionar dicho problema y al mismo tiempo no aumenta la incertidumbre en la medición.

Usando la arquitectura propuesta fue posible adicionar a un transmisor 4-20 mA los componentes necesarios para cumplir con la especificación 6.0 del protocolo de comunicación HART, con la capa física con HART Bell 202. Capa física que a su vez disminuye el límite superior de corriente consumida del lazo por la electrónica del transmisor a 3,4 mA.

La arquitectura aquí presentada tiene como ventaja adicional que debido al uso de un procesador independiente para administrar las comunicaciones digitales, puede ser utilizada para cualquier tipo de transmisor que use procesamiento digital para la señal del sensor y solo deben ser implementadas las interfaces entre estos dos procesadores.

Finalmente se pudo demostrar como la utilización del procesamiento digital de señales permitió compensar y calibrar la señal de salida de los sensores de presión piezoresistivos con un error inferior a 0,1% FS. En este caso se encontró que las características de los sensores varían en el tiempo, esos cambios aumentan el nivel de error, encontrando errores de hasta 0,3%Fs durante las pruebas. Es importante recalcar que esas modificaciones fueron del sensor y no del circuito de procesamiento de señal, por lo que se puede afirmar que la arquitectura propuesta mantiene el nivel de error del circuito original.

AGRADECIMIENTOS

Este proyecto fue desarrollado con el apoyo de la empresa MEMS Ltda. Agradecemos también a las siguientes instituciones: CNPq (Programa RHAE), FINEP (Programa de Microelectrónica), FAPESP (Programa PIPE), a los laboratorios de la EPUSP (LME y LSI) y a la Universidad del Valle (Cali-Colombia).

REFERENCIAS

1. Da Luz, S.F.: Microssistema transmissor de pressão piezoresistivo de 4-20mA de alta precisão. Dissertação de Mestrado Escola Politecnica. São Paulo, Brasil 2006.

2. Eatony, W. P. et Smith, J. H.: «Micromachined pressure sensors: review and recent developments» en Smart Materials and Structures, vol. 6, no. 5, p. 530539, Oct. 1997.

3. Jordana, J. et Pallàs-Areny, R.: «A simple, efficient interface circuit for piezoresistive pressure sensors» en Sensors and Actuators A: Physical, vol. 127, no. 1, pp. 69 73, 2006.

4. Šaponjiæ , D. et Žigic, A. : «Correction of a Piezoresistive Pressure Sensor Using a Microcontroller» en Instruments and Experimental Techniques, vol. 44, pp. 3844, 2001.

5. John, P.; Joshi, A.; Sindhanakeri, P.; Ajayakumar, P.; et Natarajan, K.: «Signal conditioner for MEMS based piezoresistive sensor» en Industrial and Information Systems (ICIIS), 2010 International Conference, 29 2010-aug. 1 2010, pp. 329 333.

6. Chuan , Y. et Chen L.: «The intelligent pressure sensor system based on DSP» en Advanced Computer Theory and Engineering (ICACTE), 2010 3rd International Conference, vol. 5, aug. 2010, pp. V5168 V5171.

7. Janusz et Bryzek: «Approaching performance limits in silicon piezoresistive pressure sensors,» en Sensors and Actuators, vol. 4, no. 0, pp. 669 678, 1983.

8. Horn, G. et Huijsing, J. H.: «Integrated Smart Sensor Calibration» en Analog Integrated Circuits and Signal Processing, vol. 14, pp. 207222, 1997,

9. Gakkestad, J.; Ohlckers, P.; et Halbo, L.; «Compensation of sensitivity shift in piezoresistive pressure sensors using linear voltage excitation» en Sensors and Actuators A: Physical, vol. 49, no. 12, pp. 11 15, 1995.

10. Akbar, M. et Shanblatt, M. A.: «Temperature compensation of piezoresistive pressure sensors» en Sensors and Actuators A: Physical, vol. 33, no. 3, pp. 155 162, 1992.

11. Zatorre, G.; Medrano, N.; Sanz, M.; Calvo, B.; Martinez, P. et Celma, S.: «Designing Adaptive Conditioning Electronics for Smart Sensing,» en Sensors Journal, IEEE, vol. 10, no. 4, pp. 831 838, abril 2010.

12. Maxim, «The MAX1463 Sensor Compensation Algorithm,» APPLICATION NOTE 2024, May 2003. [Online]. Disponible: http://www.maxim-ic.com/app-notes/index.mvp/id/2024 =0pt

13. HART Comunication Fundation, «HART Field communication Protocol Specification,» HFC_SPEC12, Revision 6.4, abril 2006.

14. Sclocchi, M.: «Input Filter Design for Switching Power Supplies,» April 2010. [Online]. Disponible: http://www.national.com/assets/en/other/National\s\do5(I)nput\s\do5(F)ilter\s\do5(D)esign\s\do5(f)or\s\do5(S)witchers.pdf =0pt

15. Maxim, «Designing a 4-20mA Current Loop Using the MAX1459 Sensor Signal Conditioner,» APPLICATION NOTE 1064, May 2002. [Online]. Disponible: http://www.datasheets.org.uk/MAX1459/Datasheet-081/DASF0036323.html =0pt

16. Maxim, «Introduction to the DS8500 HART modem,» APPLICATION NOTE 4676, Jun 2010. [Online]. Disponible: http://www.maxim-ic.com/app-notes/index.mvp/id/4676 =0pt

Recibido: Noviembre 2013

Aprobado: Enero 2014