ARTICULO ORIGINAL

Línea de Transmisión de Impulsos (TLP): Correlación con los Modelos de Descarga Electrostática (ESD)

Transmision Line Pulse (TLP): Correlation with Electrostatic Discharge Models (ESD)

Ing. Julio Guillermo Zola ; Ing. Gonzalo Andrés Pacheco

Laboratorio de Circuitos Electrónicos. Departamento de Electrónica. Facultad de Ingeniería. Universidad de Buenos Aires. Argentina.Email: jzola@fi.uba.ar; pachecogonzalo@gmail.com

]]>

RESUMEN

Existen varios modelos que intentan describir el daño que causa un evento de descarga electrostática ESD- sobre un circuito integrado CI-. El ensayo llamado Línea de Transmisión de Impulsos TLP-, resulta en particular muy utilizado para este tipo de mediciones, por lo que necesita asimismo mantener una correlación con los distintos modelos referenciados en diversos estándares, que amplíen la validez de sus resultados, Se analiza en este trabajo la búsqueda de una correlación aproximada, mediante medición y simulación con PSpice para utilizar los resultados mediante TLP, prediciendo la respuesta del dispositivo bajo prueba DUT- ante diferentes formas de onda ESD como las indicadas en los estándares.

Palabras claves: correlación, ESD, SPICE, TLP.

ABSTRACT

There are several models which try to describe the waveforms and damage produced by an electrostatic discharge event ESD- to an integrated circuit IC-. The Transmission Line Pulse TLP- test is widely used to run tests in this field, so it is needed to keep close correlation to the models used in different standards, in order to validate its results. This work analyzes the search of an approximate correlation, through tests, measurements and PSpice simulation, in order to predict, through the use of TLP information, the results of applying different standard ESD waveforms to a Device Under Test DUT-.

Key words: correlation, ESD, SPICE, TLP.

INTRODUCCION

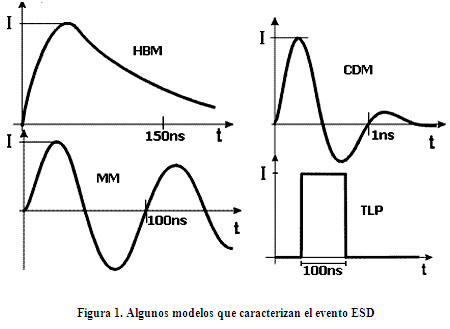

Todo circuito integrado CI- y/o dispositivo semiconductor en general DS-, es susceptible a un evento de descarga electrostática ESD-, donde las magnitudes de corrientes y tensiones involucradas son muy importantes, respecto de las que corresponden al normal funcionamiento del dispositivo [1,2]. Además, la vulnerabilidad de los DS se ve empeorada con la constante reducción de dimensiones dada por la evolución de la tecnología de fabricación. Las características del evento ESD, dependen fuertemente de los elementos que interactúen con el dispositivo, sean ellos circuitales, humanos y/o maquinaria en general. Por ello, existen distintos modelos propuestos para caracterizar estos eventos, como el modelo del cuerpo humano HBM-, modelo de máquina MM-, modelo del dispositivo cargado CDM-, etc. [3,4,5,6,7,8,9,10]. Un modelo muy utilizado en la práctica para realizar mediciones referentes a evaluar el comportamiento de un DS ante descargas electrostáticas, es la Línea de Transmisión de Impulsos TLP-, que aunque difiere de los modelos antes indicados, es una herramienta con la cual puede extraerse información de utilidad acerca del evento ESD sobre el DS [11]. Ante la no generalidad de los resultados de pruebas ESD que tienen en cuenta los modelos citados, la aplicación de estándares como el IEC 61000-4-2 [5] o el ANSI C63.16 [6], entre otros, no permiten obtener resultados que sean coincidentes y consistentes para todas las variantes que se quieran poner a prueba al DS. La figura 1 muestra las formas de onda de los modelos citados.

Sin embargo, el TLP es en la actualidad el método más utilizado para realizar pruebas de ESD sobre DS, aunque no esté aún especificado como estándar. Entonces, resulta de importancia conocer sus características para poder correlacionar los resultados que se obtengan de las pruebas con los modelos mencionados en los estándares [12,13,14]. (Figura 1).

Este método sintetiza una forma de onda cuadrada de duración y amplitud controlables, la cual no representaría en principio ninguna de las forma de onda mencionadas. A pesar de ello, el método permite aplicar señales de excitación que poseen carga eléctrica, energía específica y duración similares a las de los modelos analizados. Pero al tratarse de una señal distinta, da lugar a espectros y tiempos de transferencias distintos, que son los principales cuestionamientos presentes para la correlación de resultados con los modelos de ESD [15,16,17].

En este trabajo se analiza la búsqueda de una correlación aproximada, entre el modelo TLP y otros especificados en diversos estándares, con la finalidad de poder utilizar los resultados obtenidos mediante el sistema TLP para predecir la respuesta del DUT ante otras formas de onda ESD. Para ello se utilizará tanto la medición experimental como la simulación mediante PSpice.

]]> El TLP

Funcionamiento básico:

El TLP, cuyo esquema básico se muestra en la figura 2, genera una forma de onda cuadrada a partir de la descarga de una línea de transmisión. La línea se carga previamente mediante una fuente de alta tensión o voltaje, y luego se descarga sobre el circuito de prueba, obteniendo sobre la carga un pulso rectangular de corriente. La amplitud de la forma de onda se controla con la tensión de carga, VG, mientras que la duración del pulso se controla mediante el retardo que introduce la línea, a través de su longitud. La línea L es la que se carga con la tensión VG a través del resistor RG. El atenuador se encargará de absorber las reflexiones que se generen en el DUT.

Una forma adicional de evitar las reflexiones, es mediante el agregado de un circuito terminador formado por un diodo rápido, D, de bajo tiempo de recuperación y un resistor de 50 W en serie, tal como se indica en la misma figura. Este circuito terminador adapta la línea para un impulso negativo debido a la reflexión en el DUT. Es decir, aún en ausencia del atenuador, la línea queda suficientemente adaptada para eliminar las reflexiones.

En todo el trayecto del impulso hasta el DUT se mantiene la impedancia de la línea, Z0. Esto resulta en que todos los elementos presentes en el camino de los pulsos de tensión y corriente poseen una impedancia característica Z0: la línea L, el atenuador y todas las líneas extra que conecten el DUT e instrumental de medición (cuyas longitudes serán mucho menores a la de la línea principal, «d») [12,18]. La ventaja fundamental de esta impedancia constante, es que el pulso generado no sufre alteraciones en su forma, principalmente en su tiempo de crecimiento, debido a que transita por un sistema adaptado. Sin embargo, su tiempo de crecimiento estará limitado por la velocidad de conmutación del interruptor del sistema (llave), así como por las pérdidas que pueda haber en las líneas. Cabe mencionar, que el correcto funcionamiento del interruptor para los tiempos involucrados en el evento es un punto clave. En estos equipos generalmente se utilizan relays embebidos en mercurio, que cumplen las exigencias en los tiempos involucrados, debido a la mejora en tiempo de accionamiento y calidad de contacto libre de rebotes.

Identify applicable sponsor/s here. (sponsors)

Equipo a utilizar:

El TLP a utilizar en las mediciones corresponde al TLP50 de TLP Solutions [19]. Su diagrama en bloques básico se muestra en la figura 3. En la figura 4 puede verse un ejemplo de cómo muestra el equipo TLP50 la curva I-V correspondiente a un zener.

]]> Mediciones para pulsos de 100 ns y 200 nsSi bien se realizaron tests sobre distintos DS, tales como zeners, transistores discretos, MOSFETs de doble compuerta (gate), CIs de efecto Hall, etc., en este trabajo se mostrarán concretamente los resultados alcanzados a partir del transistor BS170 [20], correspondiente a un MOSFET de conmutación, de modo de no extender en demasía la cantidad de resultados mostrados, pero suficiente para realizar el análisis básico de correlación alcanzada, que se extiende al resto de los DS analizados.

La figura 5a muestra la curva I-V para el BS170 cuando se le aplican pulsos crecientes de 100 ns desde 0 a 1 kV. Puede observarse claramente el retroceso (snap-back) en la tensión entre drenaje (drain) y fuente (source), Vds, una vez producida la ruptura debida a un pulso VG = 840 V, aproximadamente, que provoca la destrucción del dispositivo.

La figura 5b muestra Vds (t), representada para algunos de los pulsos crecientes aplicados, obtenida por un osciloscopio de 1 Gb/s de muestreo. Puede observarse como se mantiene aproximadamente la tensión Vds en valores cercanos a la tensión de ruptura hasta alcanzar el punto de retroceso. La curva indicada con la flecha hacia abajo corresponde precisamente a dicho punto. El instante de medición sobre el pulso para la obtención de la característica I-Vds, se realiza promediando valores alrededor de los 80 ns, lejos de la zona de respuesta transitoria dada por la limitación en el ancho de banda del osciloscopio utilizado.

Estas curvas se obtuvieron para una muestra de treinta transistores, donde la dispersión entre curvas no superó el 1%. Este hecho se puede observar en el conjunto de puntos de medición de la característica I-V de la figura 6a, para los transistores utilizados. Se aseguró que los transistores bajo prueba estuviesen previamente embalados en cinta antiestática, tal como se muestra en la figura 6b, para preservar sus características originales de fabricación y evitar variaciones en sus parámetros, debidas a descargas estáticas por una manipulación incorrecta.

Tomando como válidas estas mediciones, se procedió a aplicar sobre una nueva muestra de igual número de transistores, pulsos repetitivos de 100 ns con una tensión ligeramente inferior a la que provocaba el retroceso en la característica I V. El intervalo entre pulsos puede considerarse muy superior al ancho del pulso, por lo que se admite que el dispositivo se mantiene a temperatura ambiente ante la aplicación de cada pulso. Como resultado de esta medición se obtuvieron formas de onda de Vds(t) similares a las indicadas en la figura 6, sin alcanzar en ningún caso la destrucción del dispositivo.

Posteriormente, se obtuvo la curva I-V sobre una nueva muestra, aplicando pulsos de 200 ns, para lo cual se duplicó la longitud «d» de la línea «L» indicada en la figura 2. Las curvas obtenidas fueron similares a la de la figura 5. Sin embargo, al realizar la medición utilizando pulsos repetitivos de tensión ligeramente inferior a la que provocaba el retroceso, los dispositivos se destruyeron en el primer impulso en todos los casos, observándose un forma Vds(t) como la indicada en el detalle de la figura 7 para el pulso siguiente al de la falla. Nótese que el DS termina de destruirse a los 40 ns posteriores al primer impulso de 200 ns.

]]> Estos resultados indican que la falla se está produciendo por sobre elevación de la temperatura, es decir por máxima energía absorbida. Este parámetro se tomó como base para iniciar la estimación de la correlación con las otras formas de onda que se describen para eventos ESD.Como otra forma de verificación, se modificó el pulso del TLP a una forma del modelo HBM, relevándose nuevamente la característica I-V de una muestra del BS170. El punto de retroceso no se alcanzó en el barrido hasta 1 kV y sólo se llegó a esta condición al aumentar el ancho de la onda HBM hasta casi tres veces su tiempo de decaimiento indicado en los estándares.

La figura 8a muestra la forma de onda HBM con la que se obtuvo el punto de retroceso al alcanzar un valor de 952 V, con una dispersión del 2,7 % en la muestra.

Modificándose el pulso a la forma del modelo MM, tal como se muestra en la figura 8b, nunca se alcanzó el punto de retroceso en el transistor, en un barrido hasta 1 kV.

Ambas modificaciones al circuito del TLP se logran mediante el agregado de redes del tipo R-C, para el HBM y L-C sobre la línea no adaptada, para el MM [21].

ANÁLISIS DE LA CORRELACIÓN

De acuerdo con los resultados obtenidos en las mediciones, se parte de la base que el parámetro a correlacionar es la energía o energía específica [Joule/W] transferida al DUT [22]. Se adoptará como método el ajustar la tensión VG de cada uno de los modelos para poder establecer los valores de transferencia deseados.

La energía específica que entrega cada forma de onda resulta de (ecuación 1):

]]> Admitiendo un comportamiento lineal del circuito del TLP al que se conecta el DUT, la corriente iDUT será proporcional a VG y por lo tanto, la energía específica sobre el DUT será proporcional a VG2. Por ejemplo, tomando como referencia al modelo HBM, las tensiones de carga deben variar en función de la relación (ecuación 2):Donde VGmod y Emod son la tensión de carga y la energía específica del modelo particular, a partir de los valores indicados en el estándar correspondiente. El parámetro EHBM es la energía específica del HBM y VGeq es la tensión de carga para el modelo particular que hará que su energía específica sea igual a la del HBM.

A partir de (ecuación 2), se pueden obtener los valores de VGeq para los distintos modelos. Estos valores se presentan en la Tabla 1, tomando como referencia EHBM. Asimismo, se indican los estándares correspondientes que hacen referencia a cada modelo.

La cuarta columna de la Tabla 1 indica la correlación estimada entre los diferentes modelos. Si bien este trabajo partió de mediciones con TLP, la referencia de los valores de VGeq respecto del modelo de HBM se hace teniendo en cuenta que es el modelo histórico de referencia.

Una relación de interés puede alcanzarse si se resuelve (1) en el campo de la frecuencia. (ecuación 3)

Donde I(0) = Q es la carga eléctrica inicial del circuito particular que se quiera analizar y T(ù) la función que da forma al espectro de corriente de cada modelo. Entonces: (ecuación 4)

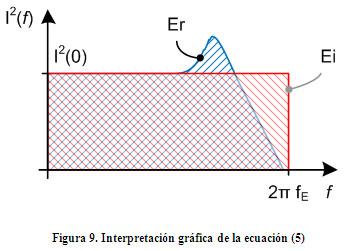

Donde, se define como Frecuencia de Igualdad Energética del respectivo modelo a (ecuación 5): (Figura 9)

Una interpretación gráfica de (ecuación 4), es la que se presenta en la figura 9, donde se observa que del espectro de I(ù)2 se puede calcular la energía específica que posee, con fE e I(0).

]]>

Gráficamente, la energía específica Er, que se obtiene a partir de considerar un modelo en particular, es el área comprendida debajo de la curva en el gráfico, obtenida mediante (ecuación 3). Utilizando (ecuación 4), la obtención de la energía específica se reduce al cálculo del área que comprende el trazo I2(0) desde f = 0 hasta fE (Ei). Por ser una constante de cada modelo, el valor de fE se lo puede calcular mediante (ecuación 4) con un solo par de valores I2(0) y E. Las fE de cada modelo, se exponen en la Tabla 2.

MODELO DE SIMULACIÓN

Para verificar los resultados de las mediciones realizadas, se utilizó el modelo indicado en la figura 10a [23], para simular con Orcad-PSpice [24] el transistor BS170. Este modelo fue ajustado en base a las mediciones realizadas mediante TLP. Si bien no se indican en la figura, se agregaron al modelo resistores de elevado valor en paralelo con las fuentes controladas que simulan los mecanismos de ruptura, para evitar problemas de convergencia que se pusieron en evidencia en algunas de las simulaciones.

Las curvas Vds(t) obtenidas resultaron similares a las medidas con TLP. En la figura 10b se observa, a modo de ejemplo, la curva I-V, hasta valores previos a la destrucción del transistor, resultante de la simulación y de la medición sobre una muestra de transistores BS170 que no se encontraban embalados en cinta antiestática (notar que la dispersión en los valores medidos aumentó al 5%). Sin embargo, aún en este caso desfavorable, la simulación sigue aproximadamente a la media de la muestra.

Estas simulaciones permitieron ajustar convenientemente los parámetros VG y fE a partir de la aplicación de las distintas ondas correspondientes a cada modelo, para obtener la correlación aproximada entre ellas.

]]> CONCLUSIONES

El análisis para obtener una aproximación de correlación entre los diferentes modelos que describen el evento ESD, se centró en un análisis semi-empírico, basado en las mediciones mediante TLP, cuyo uso es habitual para este tipo de ensayos, apoyado por el ajuste mediante simulación con Orcad-PSpice. Tanto en los valores explicitados en este trabajo, como en el resto de dispositivos ensayados, se obtuvieron relaciones similares, por lo que podría estimarse que la correlación obtenida resulta en principio válida y no tan dependiente de la tecnología del dispositivo como de la energía puesta en juego en el evento ESD.

Agradecimientos

Los autores agradecen la colaboración prestada por TLP Solutions Argentina y Cima Ingeniería SRL al permitir utilizar su equipamiento TLP50- y asesoramiento para realizar las mediciones.

REFERENCIAS

1. Vinson j. and Liou j.: «Electrostatic Discharge in Semiconductor Devices: An Overview», Proceedings of the IEEE, Vol. 86, issue 2 pp. 399-420, Feb. 1998.

2. Electrostatic Discharge Association, Rome NY: «Fundamentals of Electrostatic Discharge», http://www.esda.org/esd_fundamentals.html , 2001.

3. MIL-STD-883G: «Method 3015.7: Electrostatic Discharge Sensitivity Classification», Department of Defense Handbook Standard, 1989.

]]> 4. ANSI/ESD SP5.1.1-2006: «Standard Practice for Human Body Model (HBM) and Machine Model (MM) Alternative Test Method: Supply Pin Ganging Component Level, Electrostatic Discharge Association, 2006.5. IEC 61000-4-2 (2001-04) Ed. 1.0: «Electromagnetic compatibility (EMC)-Part 4-2: Testing and measurement techniques - Electrostatic discharge immunity test, 2006.

6. ANSI C63.16: «American National Standard Guide for Electrostatic Discharge Test Methodologies and Criteria for Electronic Equipment», 1993.

7. EIA/JESD22: «Test Method A115-A: Electrostatic Discharge (ESD) Sensitivity Testing Machine Model (MM)», Electronic Industries Association, 1997.

8. ANSI/ESD STM 5.2-1999: «Electrostatic Discharge Sensitivity Testing - Machine Model (MM) Component Level», 1999.

9. JEDEC JESD22-C101C: «Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components, 2004.

10. ESD STMS 3.1: «Charged Device Model (CDM) Component Level for Electrostatic Discharge Sensitivity Testing», Electrostatic Discharge Association , 1999.

11. Maloney t. j. and Khurana n.: «Transmission Line Pulsing Techniques for Circuit Modeling of ESD Phenomena», Proc. 7th EOS/ESD Symp., p. 49, Sep. 1985.

12. Barth j., Verhaege k., Henry l. g. and Richner j.: «TLP Calibration, Correlation, Standards and New Techniques», IEEE Transactions on Electronics Packaging Manufacturing, Vol. 24, Number 2, pp. 99-108, April 2001.

13. Hyatt h., Alonzo a. and Bellew p.: «TLP Measurements for Verification of ESD Protection Device Response», Vol. 24, Issue 2, pp. 90-98, April 2001.

14. Barth j. and Richner j.: «Correlation Considerations: Real HBM to TLP and HBM testers», Microelectronics Reliability, Volume 42, Number 6, pp. 909-917, June 2002.

15. Notermans g., de Jong p. and Kuper f.: «Pitfalls when correlating TLP, HBM and MM testing», Electrical Overstress/Electrostatic Discharge Symposium Proceedings, pp. 170-176, 6-8 Oct. 1998.

16. Stadler w., Guggenmos x., Egger p., Gieser h. and Musshoff c.: «Does the ESD-failure current obtained by Transmission-Line Pulsing always correlate to Human Body Model tests?», Electrical Overstress/Electrostatic Discharge Symposium,1997. Proceedings, pp. 366-372, 23-25 Sep 1997.

17. Huang s. c., Lee J.H., Lee S.C., Chen K.M., Song M.H., Chiang C.Y. and Mi-Chang Chang: «Circuit and Silicide Impact on the Correlation Between TLP and ESD (HBM and MM)», Integrated Reliability Workshop Final Report, 2004 IEEE InternationalPublication, pp. 169-172, 18-21 Oct. 2004.

]]> 18. Henry L. G., Barth J., Verhaege K., and Richner J.: «Transmission-Line Pulse ESD Testing of ICs: A New Beginning», Compliance Engineering, http://www.ce-mag.com/ce-mag.com/archive/01/03/0103CE_046.html , March/April 2001.19. tlp solutions: http://www.tlpsol.com/files/Download/TLP50User'sManual.pdf .

20. fairchild semiconductor: http://www.fairchildsemi.com/ds/BS/BS170.pdf .

21. Pacheco g., Zola j.: «Undamped, length varying TLP pulses measurements and ESD model approximations», Proceedings of the Argentine School of Micro-Nanoelectronics, Technology and Applications 2010, pp. 1-5, 2010.

22. Zola j., Pacheco g.: «TLP: ESD models correlation and aproximation», Proceedings of the Argentine School of Micro-Nanoelectronics, Technology and Applications 2009, pp. 93-97, 2009.

23. Zhou P., Connerney D., Carroll R., Luk T., «Modelling, Snapback and Rise-Time Effects in TLP Testing for ESD MOS devices Using BSIM3and BVIC Models», 2005 NSTI Nanotechnology Conference & Trade Show, May 2005.

24. cadence design systems: http://www.cadence.com/products/orcad/pspice_simulation/ .

]]>

Recibido: Julio 2012

Aprobado: Septiembre 2012