ARTICULO ORIGINAL

Diseño de un ASIC Sintetizador Digital Directo de alta velocidad

High Speed Direct Digital Frequency Synthesizer Asic Design

Ing. Abdel Martínez Alonso, Glauco Guillén Nieto

1 LACETEL, Cuba,Email: abdel@lacetel.cu, glauco@enet.cu

]]>

RESUMEN

El trabajo describe el proceso general de diseño y optimización de un Módulo IP para un Circuito Integrado de Aplicación Específica, destinado a la obtención de ondas cuasi-sinusoidales, empleando la técnica de Síntesis Digital Directa. El trabajo se realizó en tres etapas fundamentales: Diseño de un Sintetizador Digital Directo empleando Lenguaje de Descripción de Hardware VHDL, realizado sobre la plataforma ISE del fabricante de Dispositivos Lógicos Programables Xilinx. La plataforma ISE permite el control de todos los aspectos del flujo de diseño para la transformación de la descripción abstracta en lenguaje VHDL al nivel de bloques lógicos de un FPGA. De un total de cinco módulos diseñados, con diferentes funcionalidades y prestaciones, se registraron cuatro versiones en el Centro Nacional de Derecho de Autor (CENDA). Implementación y modelado del diseño en VHDL sobre plataforma FPGA, para la validación funcional del Módulo IP, empleando como soporte las Tarjetas de Desarrollo Spartan3E Starter Kit y ML507 del fabricante Xilinx. Adaptación del diseño a una tecnología de fabricación CMOS 0.35ìm. Se presenta un grupo de soluciones no documentadas en la literatura, basadas en principios de optimización de circuitos digitales, que posibilitan la adaptación del diseño a una tecnología específica de un fabricante dado. Dos de las versiones del Módulo IP y cinco Reportes Técnicos han sido presentados a un fabricante de Circuitos Integrados a la Medida.

Palabras claves: ASIC, DDS, módulo IP, FPGA, VHDL.

ABSTRACT

This paper describes the IP module general design process for Application Specific Integrated Circuit, intended for quasi-sine wave generation, using Direct Digital Synthesis technique. The process was carried out in three stages: The Design of Direct Digital Synthesizer employing VHDL Hardware Description Language, under ISE design platform from Xilinx. The ISE platform allows to control all aspects of VHDL to FPGA layout translation flow. During this stage, four of the five IP module versions designed with different features and functionalities were registered at the National Copyright Center (CENDA). VHDL design modeling and implementation on FPGA platform, for functional IP module validation, employing a Spartan3E Starter Kit and ML507 Evaluation Platform from Xilinx. A CMOS 0.35ìm foundry technology process design adaptation, throughout some unpublished approaches based on digital circuit optimization principles that enable specific manufacturer´s technology adaptation of the design. Two versions of IP Module and other five Technical Reports have been submitted to the ASIC manufacturer.

Key words: ASIC, DDS, IP module, FPGA, VHDL.

INTRODUCCIÓN

La Síntesis Digital Directa es un método empleado para la generación de señales cuasi-sinusoidales a partir de las muestras de amplitud almacenadas en una memoria ROM (Read Only Memory). Un integrador digital o acumulador genera la información de fase que es utilizada como direcciones para acceder a la ROM y obtener el valor de las muestras a partir de las que se conforma la forma de onda de salida deseada. [1]

Los DDS, de acuerdo al «estado del arte» en la actualidad, presentan una excelente resolución de frecuencia, pueden ser fácilmente modulados y se pueden combinar con un PLL (Phase-Locked Loop) para trasladar su rango de trabajo en el espectro de frecuencias. Con las tecnologías de fabricación de circuitos integrados actuales y el alto grado de integración, es posible realizar dispositivos DDS con adecuada pureza espectral y bajo consumo de energía, lo que hace que esta tecnología sea cada vez más empleada en aplicaciones tanto de corte académico e investigativo como comercial. [2]

El objetivo fundamental del presente trabajo es implementar un Módulo IP (Intelectual Property) para un Circuito Integrado de Aplicación Específica DDS (Direct Digital Synthesizer) capaz de generar frecuencias no inferiores a 350 MHz con un Rango Dinámico Libre de Espurias superior a 50dBc y efectuar saltos de frecuencia con demoras inferiores a 8µs. GENERALIDADES DEL DISEÑO DEL MODULO IP.

El diseño ha sido denominado LCT3212 o LCT2412 añadiendo el carácter A, B, C, D según la versión, correspondiendo a modificaciones u optimizaciones realizadas en base a requisitos del proceso de fabricación o a la incorporación de funciones. Las letras LCT son las iniciales del nombre «Laboratorio Central de Telecomunicaciones», que originó el registro de la Marca LACETEL® y constituyen el identificativo de la Entidad, Instituto de Investigación y Desarrollo de Telecomunicaciones. Los números 3212 y 2412 se corresponden con las longitudes de las palabras del Acumulador (32 ó 24 bits) y de la palabra de datos de la ROM (12 bits).

Los módulos incluyen acumuladores de 32 ó 24 bits, ROM interna de 16Kx12 bits, bloques para la reducción de niveles de espurias (Generador de Secuencia Pseudoaleatoria de 8 bits o Canal Spurkiller) así como un bloque Cuantificador. Todos los módulos se interconectan de manera que, al incorporar un conversor D/A en el bus de salida de 12 bits, se obtiene la forma de onda cuasi-sinusoidal deseada.

El Módulo IP, en todas sus variantes, provee saltos de frecuencia rápidos y una resolución de frecuencia fina (palabra binaria de sintonía de 32 bits ó 24 bits) e incorpora además perfiles de usuario con registros de 32 ó 24 bits pre-programables en cantidad de 8, característica que lo hace único dentro de los dispositivos similares existentes en la actualidad.

]]> La generación de la señal comienza por la sintonía de una determinada frecuencia, cuyo valor se encuentra en una Palabra Binaria de Sintonía FTW (del inglés, Frequency Tuning Word) que se carga mediante el interfaz de comunicación serie.Componentes generales del Módulo IP LCT3212: [3]

1) Interfaz de comunicación: Interfaz serie asíncrona, compatible con el estándar RS232 o SPI (del inglés, Serial Peripheral Interface), de acuerdo a la versión del diseño.

2) Banco de registros: Registros pre-programables, en cantidad de 8, para conservar hasta 8 valores diferentes de FTW de 32 ó 24 bits, que determinan la frecuencia de salida del DDS, en correspondencia con el Perfil de Usuario activo. Ello permite implementar saltos de frecuencia rápidos, ahorrando el tiempo necesario para cargar el registro con un nuevo valor de frecuencia a través del interfaz serie.

3) Acumulador de Fase: Componente principal del DDS, con una resolución de 32 ó 24 bits. Genera una secuencia ascendente de números binarios, cuya envolvente equivale a una rampa lineal analógica, que contiene la información de fase de la señal cuasi-sinusoidal de salida. Es un sumador realimentado que incrementa el número almacenado cada vez que recibe un pulso de reloj. La magnitud del incremento del valor del acumulador es controlada mediante la FTW.

4) Cuantificador: De esta forma se denomina (y representa como un componente) el proceso de truncado de la palabra de 32 ó 24 bits del Acumulador de Fase, para reducir el tamaño de la memoria ROM, donde se conservan las muestras de la señal de salida para cada valor de fase. El «Cuantificador» elimina de la palabra de 32 ó 24 bits del Acumulador de Fase, o sea el canal principal del DDS, los 16 u 8 bits menos significativos, según la versión. El inconveniente de esta denominada «cuantificación» es la introducción de ruido de fase cuyo valor máximo es de 5.5x10-3 grados en una rotación de 360 grados equivalente a un período de la onda sinusoidal.

5) Memoria ROM: Tiene un tamaño de 16Kx12 bits, en ella se realiza la operación de conversión fase-amplitud. A esta memoria suele denominársele «lookup table» (LUT). En este bloque es donde a cada uno de los valores discretos de fase se le hace corresponder un valor de amplitud de una sinusoide. La LUT sólo utiliza los 16 bits de mayor peso o más significativos de la salida del Acumulador, si manejara la totalidad de los bits de salida del acumulador de fase, las dimensiones de la ROM serían demasiado grandes. El tamaño de la ROM ha sido reducido, en aproximadamente un 75%, al emplear tablas más pequeñas, almacenando solamente 1/4 de la señal sinusoidal e incorporando lógica adicional para obtener el ciclo completo.

Para reconstruir la onda completa entre 0 y 2ð se utilizan los dos bits de mayor peso, es decir, los dos MSB del Acumulador de Fase, el primero de ellos, para fijar el signo, mientras que el segundo resuelve si la pendiente del seno va a ser creciente o decreciente. Con ésta solución se utilizan como entradas de la ROM solo 14 de los 16 bits del Acumulador de Fase, hecho que conduce a una reducción de 4:1 del tamaño de la ROM. Este método reduce significativamente el consumo de recursos del FPGA o ASIC por concepto de memoria ROM.

6) Bloque de reducción de niveles de espuria: Difuminador de Fase de 8 bits o Canal Spurkiller, según la versión.

]]> PERFILES DE USUARIO

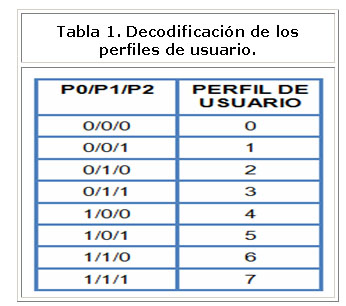

Están conformados por un grupo de registros del banco de memoria con una función específica. En cada Perfil de Usuario del LCT3212 o LCT2412 se almacena una palabra binaria de Sintonía FTW. Uno de los Perfiles de Usuario es seleccionado cada vez, a través de la decodificación de los estados lógicos aplicados a tres pines de entrada (P1, P2 y P3) según se define en la Tabla 1. De esta forma es posible realizar un cambio rápido de los parámetros del DDS, a través de la conmutación entre Perfiles de Usuario, lo cual elimina las demoras que impondría la transmisión de datos cada vez a través del puerto de comunicación serie. [3]

SINCRONIZACIÓN DEL SISTEMA

La señal de reloj del sistema se suministra a través del correspondiente pin de entrada, como referencia para el trabajo sincronizado de todos los componentes y la obtención de la frecuencia de salida del DDS, de acuerdo a la Ecuación 1: [4]

Donde:

]]> FTW: Palabra Binaria de Sintonía.REFCLK: Frecuencia del reloj del sistema.

N: Cantidad de bits del Acumulador.

La resolución de frecuencia se obtiene en función de la frecuencia de reloj del sistema y la cantidad de bits del acumulador. Puede ser determinada utilizando la Ecuación 2: [4]

Donde:

REFCLK: Frecuencia del reloj del sistema.

N: Cantidad de bits del Acumulador.

PARTICULARIDADES DE LAS VERSIONES

]]> LCT3212A: MÓDULO IP PARA UN SINTETIZADOR DIGITAL DIRECTOCaracterísticas Principales: [5]

· Interfaz de Comunicación RS232.

· Memoria ROM interna de 16kx12.

· Registro Acumulador de 32 bits.

· 8 Perfiles de Usuario con registros de 32 bits pre-programables.

· 12 bits de resolución de salida.

DESCRIPCIÓN DEL FUNCIONAMIENTO

El módulo LCT3212A está compuesto por los módulos digitales básicos de un Dispositivo DDS: Acumulador de Fase (sumador realimentado) y el PWC (del inglés Phase to Waveform Converter) que es una tabla de muestras, implementada en una memoria ROM (Figura 1).

]]> Accediendo con incrementos lineales de direcciones a una tabla de valores con las muestras de amplitud de un cuarto de período de una sinusoide, se genera una representación digital de la señal deseada a partir de una única señal de referencia. La posterior conversión a una señal analógica se realiza con un conversor D/A. [5]

INTERFAZ DE COMUNICACIÓN RS232

El puerto de comunicación serie RS232 diseñado consta de 2 pines para la recepción y transmisión de los datos DTI y DTO respectivamente. El pin DTI opera como la entrada, y el pin DTO como salida de datos serie. Ambos pines son compatibles a nivel lógico con el protocolo del estándar RS232. [5]

El intercambio de datos en la comunicación serie se divide en dos fases: la Fase 1 es un ciclo de instrucción consistente en el envío de una palabra de 8 bits. El bit más significativo (MSB) de la palabra de instrucción identifica la operación a realizar como de escritura o de lectura, los 6 bits menos significativos (LSBs) se utilizan para indicar la dirección del registro. El bit correspondiente a la posición D6 queda reservado para futuras aplicaciones. [5] (Tabla 2)

Durante la Fase 2 la información es enviada desde o hacia el registro direccionado. El byte de datos contiene parte de la información de la FTW, la cual será almacenada o leída según corresponda. Para lograr una correcta operación de transferencia o lectura de datos es necesario que se transmita la totalidad de los bits comprendidos en ambas fases. [5]

La transmisión serie emplea un formato de paquetes de 8 bits (Figura 2). Los bits son transmitidos de forma asíncrona con 1 bit de inicio y 1 bit de parada, de B1 a B8, siendo B8 el bit más significativo (MSB) y B1 el menos significativo (LSB). No se utiliza chequeo de paridad. [5]

LCT3212B: MÓDULO IP PARA UN SINTETIZADOR DIGITAL DIRECTO UTILIZANDO DIFUMINADO DE FASE

Características principales: [6]

]]> · Interfaz de comunicación serie RS232.· Memoria ROM interna de 16kx12.

· Registro Acumulador de 32 bits.

· 8 Perfiles de Usuario con registros de 32 bits pre-programables.

· 12 bits de resolución de salida.

· Reducción de niveles de espurias mediante difuminado de fase.

DESCRIPCIÓN DEL FUNCIONAMIENTO

El Módulo LCT3212B (Figura 3) hereda todas las características básicas del Módulo LCT3212A, por lo que las descripciones del funcionamiento, interfaz de comunicación, banco de registros y formato para el intercambio de mensajes del LCT3212A son aplicables al módulo LCT3212B. [6]

Adicionalmente a los módulos presentes en el LCT3212A, el LCT3212B posee dos modificaciones fundamentales:

]]> · Adición de un bloque para el difuminado de la fase.· Incorporación de señales de control de sincronía del Interfaz de Comunicación.

BLOQUE DIFUMINADOR DE FASE

Está compuesto por un generador de secuencia pseudoaleatoria (Figura 4) encargado de «inyectar» una secuencia de pseudorruido para mejorar el SFDR (Rango Dinámico Libre de Espurios) del espectro a la salida del sintetizador. [7]

Para garantizar no caer en el estado de bucle, se carga durante el ciclo de reset inicial un valor lógico «1» en el registro D1 y un valor «0» en el resto (01H). De esta manera se evita la generación indefinida de valores de «0» en los correspondientes lazos de realimentación del LFSR.

La señal aleatoria denominada «dither» es una secuencia de ruido con una varianza aproximadamente igual al peso del bit menos significativo de los 16 tomados como bus de entrada del bloque PWC. Esta secuencia es añadida a la señal de salida del acumulador antes de ingresar al bloque Cuantificador. Al utilizar esta técnica es posible mejorar el SFDR en aproximadamente 12dB en comparación con un diseño que no contara con un método de reducción de niveles de espurias. [7] Los recursos lógicos adicionales requeridos para la implementación de este bloque no resultan significativos, comparados con los recursos empleados por el resto del diseño.

La principal ventaja obtenida al emplear la técnica de difuminado de fase es que la estructura de líneas indeseadas en el espectro de la señal de salida desaparece, apareciendo en su lugar un piso de «ruido blanco» Generalmente este ruido resulta menos inconveniente que la aparición de espurias, por ejemplo, en aplicaciones como los receptores digitales que emplean DDS como generadores de señal en las etapas de mezcla. [7]

LCT3212C: MÓDULO IP PARA UN SINTETIZADOR DIGITAL DIRECTO UTILIZANDO LA TÉCNICA SPURKILLER PARA LA REDUCCIÓN DE NIVELES DE ESPURIAS

]]> Características principales: [8]· Interfaz de comunicación serie RS232.

· Memoria ROM del Canal Principal de 16kx12.

· Memoria ROM del Canal SpurKiller de 1kx6.

· Registro Acumulador de 32 bits.

· 8 Perfiles de Usuario con registros de 32 bits pre-programables.

· 12 bits de resolución de salida.

· 2 canales SpurKiller para la reducción de niveles de espurias.

DESCRIPCIÓN DEL FUNCIONAMIENTO DEL MÓDULO IP LCT3212C

]]> El canal principal del Módulo IP tiene las mismas prestaciones del Módulo LCT3212A. Se sustituye el bloque Difuminador de Fase empleado en el módulo LCT3212B por dos canales SpurKiller con el mismo objetivo de mejorar la pureza espectral del sistema. Debido a la adición de estos canales se incorporan varios registros de control y configuración (Figura 5). [8]

CANALES SPURKILLER

Los canales para la reducción de espurias están compuestos por bloques DDS sintonizados a la frecuencia de la espuria que se desea eliminar. La señal de salida de cada Canal DDS Spurkiller es sumada en contrafase con la del Canal DDS Principal, con el objetivo de eliminar la línea espectral correspondiente a la espuria. La señal resultante de la sumatoria es la que ingresa al Conversor Digital-Analógico. [9]

Los errores de linealidad y cuantificación provocan líneas indeseadas en el espectro de salida de un DDS, en detrimento del SFDR. La arquitectura del módulo LCT3212C permite reducir al máximo el nivel de una determinada línea espectral indeseada por cada uno de los canales SpurKiller que posee, resultando en una mejora selectiva del SFDR. La arquitectura del DDS se basa en el método de Interferencia Destructiva, el cual consiste en la pre-distorsión de la señal digital, antes de su entrada al DAC, de tal forma que se elimine o reduzca sustancialmente el nivel de una específica de las señales espurias por cada canal SpurKiller disponible. [9]

El fundamento de la técnica empleada para el diseño del Módulo LCT3212C consiste en combinar la señal original con una réplica de una señal espuria específica que se desea eliminar (misma amplitud y frecuencia) pero desfasada 180°. [9]

LCT2412A: MÓDULO IP PARA UN SINTETIZADOR DIGITAL DIRECTO CON INTERFAZ SPI

Características principales:

· Interfaz de comunicación serie SPI.

]]> · Memoria ROM interna de 16kx12.· Registro acumulador de 24 bits.

· 8 perfiles de usuario con registros de 24 bits pre-programables.

· 12 bits de resolución de salida.

· Reducción de niveles de espurias mediante difuminado de fase.

DESCRIPCIÓN DEL FUNCIONAMIENTO

El Módulo LCT2412A (Figura 6) hereda las características básicas del Módulo LCT3212B, por lo que las descripciones del funcionamiento son aplicables al módulo LCT2412A.

Se sustituye el Interfaz de Comunicación RS232, utilizado en las versiones anteriores, por un interfaz SPI y se incorpora una estructura de «pipeline» balanceada en un canal principal con Acumulador de 24 bits, con el objetivo de reducir las demoras de la lógica combinacional .

]]> INTERFAZ SPI

El bloque SPI incluye: línea de reloj, entrada de datos, salida de datos y un pin de selección (Figura 7). La principal ventaja de emplear el interfaz SPI, en lugar de RS232, es que se reduce el número de compuertas equivalentes y en consecuencia, el consumo energético y área del circuito integrado final, disminuyendo el costo de fabricación, montaje y puesta en marcha de la aplicación. El formato de transmisión consta de 3 bits de direccionamiento, empleados para indicar el registro del DDS en que deberán ser almacenados los siguientes 24 bits de la cadena que corresponden a la Palabra de Sintonía de Frecuencia. [3]

La sustitución del interfaz RS232 por SPI brindará al sistema algunas ventajas adicionales:

· No está limitado a la transferencia de bloques de 8 bits.

· Implementación en hardware relativamente simple.

· Menor consumo de energía debido a que posee menos compuertas equivalentes.

Desventajas fundamentales:

· El protocolo SPI sólo funciona en distancias relativamente cortas, comparado con RS232.

· No puede ser conectado directamente a PCs, pues estas generalmente no poseen interfaces SPI compatibles.

]]> ESTRUCTURA DE «PIPELINE» BALANCEADA

A partir de los resultados de las simulaciones y análisis de tiempo de los diseños anteriores, es necesario disminuir las demoras de la lógica combinacional para poder incrementar la frecuencia de trabajo.

Causas fundamentales que provocan la disminución de la frecuencia efectiva de trabajo: [10]

· El empleo de librerías con componentes que presentan grandes demoras: En este caso la única solución posible es el empleo de librerías basadas en tecnologías de fabricación más avanzadas. Esta solución es altamente dependiente de las posibilidades tecnológicas del fabricante seleccionado y totalmente fuera del alcance del diseño a nivel RTL.

· Bloques de lógica combinacional demasiado complejos: Este elemento está directamente relacionado con el diseño en lenguaje HDL y puede minimizarse empleando técnicas de optimización del diseño digital.

Con el objetivo de aumentar la frecuencia efectiva de trabajo se aplicaron dos técnicas de diseño digital:

· Balance de Registros: Consiste en reposicionar los registros dentro de la lógica combinacional, de forma tal que se logre un equilibrio en las demoras de todos bloques combinacionales (Figura 8). [10]

· Pipelining: Este método, a diferencia del anterior, varía el comportamiento del diseño. La idea consiste en insertar registros dentro de la estructura de lógica combinacional que mayor demora presente (Figura 9). De esta manera se disminuye la lógica entre registros a expensas del incremento de la latencia del sistema, pues los datos aparecerán en la salida varios pulsos después, en comparación con el diseño original. [10]

El módulo LCT2412A posee una estructura de 10 etapas de pipeline balanceadas, lo cual implica una latencia de 10 pulsos de reloj.

El diseño fue sintetizado en 3 alternativas con librerías diferentes: del fabricante de circuitos integrados a la medida Belmicrosystem, Spartan-3E de Xilinx y SCL05u del fabricante Semi-Conductor Laboratory (SCL). En todos los casos se analizó el diseño a nivel de diagrama RTL evidenciándose diferencias sustanciales en los circuitos generados por las diferentes herramientas de síntesis.

]]>LCT2412B: MÓDULO IP PARA UN SINTETIZADOR DIGITAL DIRECTO CON INTERFAZ SPI

Características principales: [11]

· Interfaz de comunicación serie SPI.

· Memoria ROM interna de 16kx12.

· Registro Acumulador de 24 bits.

· 8 Perfiles de Usuario con registros de 24 bits pre-programables.

· 12 bits de resolución de salida.

DESCRIPCIÓN DEL FUNCIONAMIENTO

]]> El Módulo LCT2412B (Figura 10) hereda todas las características básicas del Módulo LCT2412A, excluyendo la atenuación de espurias utilizando difuminado de fase. Es optimizado con el objetivo de logar un diseño capaz de trabajar a mayor frecuencia de reloj.

BLOQUE ACUMULADOR

El bloque Acumulador es diseñado con una estructura de «pipeline», que consta de un sumador simple de 1 bit, 22 etapas de sumadores completos de 1 bit y un sumador sin salida de acarreo de 1 bit (Figura 11).

La estructura del Bloque Acumulador se basa en un canal de «pipeline» dispuesto de manera tal que la demora máxima de la lógica combinacional se encuentra en los bloques de sumadores, los cuales poseen salidas y entradas registradas. De esta manera el sumador será capaz de trabajar a la frecuencia cuyo período es equivalente a la demora del bloque sumador combinacional más lento. [11]

El diseño del Bloque Acumulador fue sintetizado empleando una librería del fabricante de Circuitos Integrados de Aplicación Específica Belmicrosystem, para un proceso de fabricación de 0.35um. A partir del análisis de tiempo realizado, con el software LEONARDO SPECTRUM VERSION 2007a.37, el diseño posee una demora máxima de 2.31ns y es capaz de trabajar a una frecuencia de reloj máxima de 432.8 MHz.

MEMORIA ROM

La memoria ROM constituye el bloque de mayor complejidad y, por tanto, el de mayores demoras, limitando significativamente la frecuencia de trabajo del sistema en su conjunto.

Los módulos LCT3212A, LCT3212B, LCT3212C y LCT2412A poseen un diseño de memoria basado en el mapeo de un cuarto de onda de la señal sinusoidal, reduciendo considerablemente la cantidad de compuertas equivalentes empleadas en comparación con un diseño que almacenara la onda completa. No obstante, los compiladores al implementar los bloques de memoria generan largas cadenas combinacionales que provocan demoras excesivas.

]]> Un primer acercamiento al rediseño de la Memoria ROM fue la implementación de una estructura de bloques de memoria de pequeña capacidad con salida multiplexada (Figura 12). De esta manera se concentra la lógica combinacional en los pequeños bloques de manera que, al registrar tanto sus entradas de datos como sus salidas hacia el multiplexor, se logra un incremento en la frecuencia de trabajo.La tabla de búsqueda fue subdividida en 16, 32 y 128 sub-bloques de memoria, optimizándose hasta alcanzar la frecuencia de trabajo de 110.5 MHz sintetizando el diseño con la librería del fabricante Belmicrosystem. A partir de la subdivisión en 128 bloques, las demoras que presenta el multiplexor de salida comienzan a convertirse en el camino crítico dentro de la lógica combinacional, por lo que no tiene sentido continuar subdividiendo el sistema. [11]

Un diseño alternativo a los analizados con anterioridad fue implementado partiendo de la Tabla de la Verdad de cada uno de los bits de salida, a partir de los bits del bus de direcciones de la ROM. Cada tabla de funcionamiento es expresada como suma de productos en la forma canónica de una función lógica.

Utilizando el software SIS (Sequential Interactive Synthesis), desarrrollado por la Universidad de Berkeley en California, Estados Unidos, se obtienen las sumas de productos de cada bit de salida (Figura 13) a partir de la información de la Tabla de la Verdad correspondiente.

Las funciones lógicas de cada uno de los 12 bits de salida de la ROM, expresadas como suma de productos, fueron implementadas empleando compuertas AND y OR. Cada salida de una etapa de suma dentro de la función lógica fue registrada, creándose una estructura de «pipeline» dentro de la memoria ROM, en la que las cadenas de lógica combinacional son limitadas a un bloque de dos etapas de multiplicación registradas implementado con compuertas AND, seguida de una compuerta OR de dos entradas, con la que se implementa la suma (Figura 14).

El diseño fue sintetizado en las 3 alternativas con librerías diferentes: del fabricante Belmicrosystem, Virtex-5 de Xilinx y SCL05u del fabricante Semi-Conductor Laboratory (SCL). El análisis del diseño a nivel de diagrama RTL confirmó que los circuitos generados por las diferentes herramientas de síntesis son más sencillos y regulares en el caso de la ROM expresada como suma de productos que en las versiones basadas en bloques de memoria de pequeña capacidad con salida multiplexada.

VALIDACIÓN Y VERIFICACIÓN FUNCIONAL

]]> La verificación funcional de cada una de las versiones se realizó en tres etapas fundamentales:1. Simulación funcional del diseño VHDL mediante la herramienta ModelSim de Mentor Graphics. Evaluación de los resultados del comportamiento lógico del diseño.

2. Simulación y Análisis de Tiempo empleando las herramientas LEONARDO SPECTRUM VERSION 2007a.37 de Mentor Graphics y Timing Analizer de Xilinx. Se incluye información de temporizado de la síntesis sobre diferentes tecnologías de ASICs.

3. Implementación y modelado sobre plataforma FPGA Spartan-3E y Virtex-5 de Xilinx.

SIMULACIÓN FUNCIONAL DEL DISEÑO

La simulación es el proceso de evaluar el comportamiento de un sistema a partir de un modelo de éste. En la etapa inicial de la simulación se valida el modelo respecto al sistema real que representa. Luego, la simulación permite realizar numerosas pruebas en un corto tiempo y sin exponer al sistema real, lo que permite perfeccionarlo y optimizarlo.

Una vez finalizada la etapa del diseño correspondiente a la programación en Lenguaje de Descripción de Hardware - VHDL, se pasa a la comprobación del código, empleando la herramienta ModelSim de Mentor Graphics.

ModelSim es un entorno de modelización y simulación que permite la verificación de los diseños generados en código VHDL. Durante la simulación, se identifican errores u omisiones, se retorna a etapas anteriores del proceso y se realizan los cambios pertinentes.

Se efectuó la simulación de cada bloque del DDS, de manera individual y sobre el sistema en su conjunto. A continuación se muestran algunas simulaciones del Módulo LCT2412B:

]]> · Figura 15: Correcta recepción de cadenas de datos SPI, correspondientes a 3 bits de direccionamiento empleados para indicar el registro del DDS en que deberán ser almacenados los siguientes 24 bits de la Palabra de Sintonía de Frecuencia.· Figura 16: Señal de salida del Acumulador de Fase. Secuencia ascendente de números binarios cuya envolvente equivale a una rampa lineal analógica. Contiene la información de fase de la señal cuasi-sinusoidal de salida.

· Figura 17: Latencia del sistema. Cambio de la frecuencia de salida del DDS a través de la conmutación entre Perfiles de Usuario. El Módulo LCT2412B posee 55 etapas de pipeline balanceadas, lo cual implica una latencia de 55 pulsos de reloj.

· Figura 18: Generación, a partir de una única señal de referencia de frecuencia fija, de una representación digital de la señal sinusoidal.

ANÁLISIS DE TIEMPO

Para el análisis de las demoras en el diseño se emplearon las librerías de los fabricantes de ASICs Belmicrosystem y Semi-Conductor Laboratory (SCL), basadas en tecnologías CMOS de 0.35µm y 0.5µm respectivamente y las librerías del fabricante de FPGAs Xilinx para las familias Spartan-3E y Virtex-5, basadas en tecnologías CMOS de 90nm y 65nm respectivamente.

A partir del análisis de tiempo realizado, empleando las herramientas LEONARDO SPECTRUM VERSION 2007a.37 de Mentor Graphics y Timing Analizer de Xilinx, se obtuvieron los siguientes resultados:

]]> La Tabla 3 evidencia una progresión en los resultados obtenidos. Se logró alcanzar la frecuencia de trabajo de 250 MHz implementando el Módulo IP LCT2412B sobre un FPGA de bajo desempeño (XC5VFX70T-1FFG1136) de la familia Virtex-5.De acuerdo a los resultados revelados por el análisis de tiempo, es posible obtener un DDS capaz de generar una frecuencia de salida máxima de 112MHz empotrando el Módulo IP LCT2412B en un FPGA Virtex-5 de bajo desempeño. En la literatura se reporta la comprobación práctica que evidencia que se logran velocidades de trabajo, como promedio, 4,6 veces superiores en un ASIC que en un FPGA de bajo desempeño. [12]

El Módulo IP LCT2412B empotrado en un FPGA Virtex-5 alcanza una frecuencia de salida máxima de 112MHz. Ello permite esperar que su implementación en un ASIC, con tecnología CMOS 65nm, alcance frecuencias de salida superiores a 350 MHz, con un incremento de velocidad de solo 3,1 veces contra el promedio de 4,6 que puede obtenerse. [12]

IMPLEMENTACIÓN Y MODELADO DEL MÓDULO IP SOBRE PLATAFORMA FPGA. VERIFICACIÓN FUNCIONAL

Como soporte para la implementación del diseño se emplearon las plataformas Spartan-3E y Virtex-5 de Xilinx las cuales constituyen un medio idóneo para la emulación y verificación de prototipos de ASIC. El hardware empleado fue Tarjetas de Desarrollo Spartan-3E Starter Kit y ML507 Evaluation Platform, de acuerdo a la versión del Módulo IP a verificar (Figura 19).

Se realizaron mediciones con el objetivo de comprobar las características espectrales de la señal de salida (Figura 20).

]]> En el caso del módulo LCT2412B se midió directamente la señal de salida del DAC sin emplear un Filtro Pasa-Bajos. En todos los casos fue empleado un Conversor Digital Analógico basado en una matriz R-2R discreta. La dispersión de los valores de las resistencias empleadas provoca un incremento del nivel de los armónicos indeseados.Además, se realizaron mediciones con el objetivo de evaluar las demoras del sistema durante los saltos de fase implementados mediante la conmutación entre Perfiles de Usuario.

De acuerdo a los resultados obtenidos mediante la verificación funcional del sistema, es posible obtener un DDS con un Rango Dinámico Libre de Espurias superior a 50dBc que efectúe saltos de frecuencia configurables en toda la banda de trabajo con demoras constantes que corresponden a una latencia de 55 pulsos de reloj. La Figura 21 muestra la demora de 220ns para una frecuencia de reloj de 250MHz.

CONCLUSIONES

Diseñados y validados 5 Módulos IP para igual cantidad de variantes de DDS, implementándose en las Tarjetas de Desarrollo Spartan3E y ML507 para su comprobación. En las pruebas realizadas se validó el correcto funcionamiento de los diseños y la repetitividad en las mediciones.

Diseñado un Módulo IP capaz de generar una frecuencia máxima de salida de 112MHz empotrado en un FPGA Virtex-5 de bajo desempeño. Ello permite esperar que su implementación en un ASIC, con tecnología CMOS 65nm, alcance frecuencias de salida superiores a 350 MHz, con un incremento de velocidad de solo 3,1 veces contra el promedio de 4,6 que puede obtenerse. [12]

Aplicadas y validadas técnicas de reducción de niveles de espurias, comprobándose su efectividad. Obtenido un Rango Dinámico Libre de Espurias superior a 50dBc.

Diseñado un Módulo IP capaz de efectuar saltos de frecuencia configurables en toda la banda de trabajo con demoras constantes inferiores a 8µs.

Enviadas al «foundry» (fábrica de Circuitos Integrados) 2 versiones de Módulo IP para su análisis y evaluación de factibilidad de fabricación utilizando tecnología CMOS 0.35ìm.

]]> Aplicadas novedosas variantes de optimización de diseños digitales, adquiriéndose una experiencia valiosa en el conocimiento de los procesos de fabricación de Circuitos Integrados a la Medida, permitiendo acercarse al límite potencial de la tecnología empleada.

REFERENCIAS

1. Bar-Giora Goldberg. Digital Frequency Synthesis Demystified. Cap. 4, Pág. 89. LLH Technology Publishing, 1999. ISBN 1-878707-47-7

2. Hernández, Rolando y Guillén, Glauco. «Síntesis digital directa de señales con reloj único». LACETEL (1991). Ciudad de la Habana. [En línea]. Disponible en: http://www.lacetel.cu

3. LACETEL (2011). Diseño de un Módulo IP para un ASIC Sintetizador Digital Directo. INFORMÁTICA 2011. Ciudad de la Habana. [En línea]. Disponible en: http://www.informaticahabana.cu/node/1633

4. Analog Devices (1999). A Technical Tutorial on Digital Signal Synthesis. [En línea]. Disponible en: http://www.analog.com.

5. LACETEL (2009). DDS IP Module LCT3212A VHDL. Soft-Intellectual Property Module. Ciudad de la Habana. [En línea]. Disponible en: http://www.lacetel.cu

6. LACETEL (2009). PD-DDS IP Module LCT3212B VHDL. Soft-Intellectual Property Module. Ciudad de la Habana. [En línea]. Disponible en: http://www.lacetel.cu

]]> 7. XILINX. (2005). Logicore DDS v5.0. Disponible en: http://www.xilinx.com8.LACETEL (2009). SK-DDS IP Module LCT3212C VHDL. Soft-Intellectual Property Module. Ciudad de la Habana. [En línea]. Disponible en: http://www.lacetel.cu.

9. Ken Gentile, Roger Huntley. Signal Cancellation Improves DDS SFDR. Agosto 2006. . [En línea]. Disponible en: http://www.mwrf.com.

10. A. Wich, «ASIC Direct Digital Synthesis circuit design,» Task of Master of Science Thesis, Faculty of Electrical Engineering, Czech Technical University in Prague 2008.

11. LACETEL. (2011). LCT2412B: Módulo IP para un Sintetizador Digital Directo con interfaz SPI basado en lenguaje VHDL. Disponible en: http://www.lacetel.cu

12. I. Kuon y J. Rose. (2007). Measuring the Gap Between FPGAs and ASICs. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 26. Disponible en: http://citeseerx.ist.psu.edu/viewdoc/download?doi=10.1.1.79.1366&rep=rep1&type=pdf

]]> Recibido: Julio 2012

]]>