Red de Procesadores Evolutivos para solucionar el Problema de los Tres Colores. Implementación en Hardware

Network of Evolutionary Processors to solve the Problem of the Three Colors. Hardware Implementation

José A. Castaño1*, Valery Moreno2, Alejandro Cabrera2, Abraham Gutiérrez3 y Víctor Martínez3

1 Universidad de las Ciencias Informáticas. Carretera a San Antonio de los Baños, km 2 ½, Torrens, Boyeros, La Habana, Cuba. CP.: 19370. ]]>

2 Instituto Superior Politécnico José Antonio Echeverría. Cuba.

3 Universidad Politécnica de Madrid, España.

* Autor para correspondencia: joseantonio@uci.cu

RESUMEN

En este trabajo se diseña una Red de Procesadores Evolutivos (NEP) para solucionar el Problema de los Tres Colores. Para obtener el resultado, se utilizó como recurso de Hardware un FPGA. El objetivo principal de este trabajo, es demostrar la factibilidad de la implementación física de algoritmos paralelos para solucionar problemas NP – Completos. Con esta implementación se logra que la ejecución de la solución al problema se haga de forma fiable, rápida y eficaz. El proyecto fue desarrollado usando la herramienta ISE 12.1 de Xilinx, utilizando como lenguaje de descripción de hardware al VHDL. Para la simulación se utilizó la herramienta ISim 12.1, también de Xilinx. Los resultados fueron probados utilizando la plataforma Atlys Board de la compañía Digilent la cual contiene un FPGA Spartan-6 LX45, también de Xilinx. Se muestran imágenes de la herramienta empleada, del Kit de Pruebas, así como de la simulación realizada y una tabla con los datos que demuestran que la implementación de este algoritmo complejo utilizó muy pocos recursos del FPGA empleado.

Palabras clave: NEP, FPGA, VHDL, Algoritmos Paralelos, Problemas NP Completos.

ABSTRACT

]]> In this paper, a Network of Evolutionary Processors (NEP) is implemented, to solve the problem of the three colors. To achieve implementation, it was used as an FPGA hardware resource. The main objective of this work is to demonstrate the feasibility of the physical implementation of parallel algorithms to solve problems NP - complete. With this implementation is achieved that the implementation of the solution to be made reliably, quickly and efficiently. The project was developed using the Xilinx ISE 12.1 tool, using hardware description language to VHDL. For the simulation tool was used ISim 12.1, also from Xilinx. The results were tested using the platform Atlys Board Company which contains a Digilent Spartan-6 LX45 FPGA, Xilinx also. Images of the tool used, the Test Kit and simulation performed and a table of data showing that the implementation of this complex algorithm used very few FPGA resources used are shown.

INTRODUCCIÓN

La implementación de algoritmos complejos en hardware, ha sido una de las tareas más desarrolladas por los investigadores del campo de los Sistemas Digitales. (Martínez, 2008) La necesidad de ejecutar algoritmos con rapidez, fiabilidad y bajos costos ha sido un factor determinante en el desarrollo de implementaciones en hardware. La aparición de circuitos integrados reconfigurables, que permiten la ejecución paralela de señales, ha permitido la implementación física de los mencionados algoritmos (Castaño, 2014), como son los FPGA (Field Programable Gate Array – Campo Programable de Arreglos de Compuertas).

El desarrollo de aplicaciones sobre los FPGA se realiza a partir de diversas técnicas, siendo la más utilizada, la descripción del hardware mediante algún lenguaje. En este proyecto se utilizó el lenguaje VHDL (Ashenden, 1990), por su sencillez y por la rapidez con se pueden desarrollar los proyectos, en particular el diseño de las Redes de Procesadores Evolutivos (NEP – Network Evolutionary Processors).

]]>

La NEP diseñada tiene como fin brindar solución al conocido Problema de los Tres Colores [Díaz, 2008], pues permite dividir el problema complejo en varios de menor complejidad y solucionarlos de forma paralela. Este problema consiste en decidir cómo colorear cada uno de los vértices de un grafo, empleando tres colores de tal manera que después de colorearlos no existan dos vértices conectados por una arista con el mismo color.

El problema a resolver es clasificado como NP – Completo y su complejidad radica en que la solución presenta un tiempo exponencial, debido a que el algoritmo de solución se realiza de forma secuencial. Una forma de solucionarlo es procurar su solución en tiempo polinomial, de ahí la necesidad de implementarlo de forma paralela, para lo cual los FPGA son ideales.

MATERIALES Y MÉTODOS

En este apartado, se exponen los elementos característicos de los FPGA, el Lenguaje VHDL y el Problema de los Tres Colores. Además, se documenta toda la teoría asociada con las Redes de Procesadores Evolutivos, con el objetivo de facilitar la compresnsión de la solución final.

Hardware reconfigurable: FPGA

Los FPGA son circuitos integrados que tienen una estructura interna que permite ser configurada por los usuarios, con la intención de implementar funciones digitales de complejidad diversa. Son reconfigurables, lo que permite que sean programados siempre que sea necesario, sin tener que cambiar la arquitectura del sistema en el que se encuentren. [Ramírez, 2011] ]]>

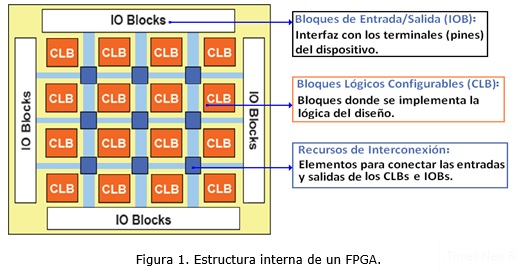

Están formados básicamente por Bloques de Entrada/Salida (IOB), Bloques Lógicos Configurables (CLB) y Recursos de Interconexión (IR). Los IOB (Input/Output Block), se encargan de la comunicación de los componentes internos del dispositivo con el exterior, a través de los terminales (pines). En los CLB (Configurable Logic Block) es donde se implementa la lógica del diseño realizado. Los IR (Interconection Resources) son los elementos que permiten conectar a los IOBs y a los CLBs. ( Ver figura 1)

La utilización de los FPGA en lugar de otra arquitectura, se basa en cinco factores: la velocidad de trabajo del sistema diseñado, la flexibilidad del hardware reconfigurable, la reducción de costos, el bajo consumo de energía y la fiabilidad del producto final.

Para implementar un sistema digital sobre un FPGA, el mismo se programa a partir de la descripción de sus componentes en un HDL. Se debe utilizar el Entorno de Desarrollo que provea el fabricante de la FPGA a utilizar y este se encargará de la síntesis del diseño, implementación y generación del fichero de programación del dispositivo.

Lenguaje de descripción de hardware VHDL

El Lenguaje de Descripción de Hardware que se utiliza para la implementación de la NEP sobre un FPGA es el VHDL. Proviene de VHSIC – HDL (Very High Speed Integrated Circuit – Hardware Description Language). Está diseñado para describir la funcionalidad y la organización de sistemas digitales utilizando un lenguaje formal. (Freire, 2011)

Se redacta como texto y posee una sintaxis amplia y flexible. No es práctico tratar de conocerlo completo antes de usarlo, conociéndolo sólo parcialmente se resuelven muchos problemas. Sus principales características son (Castaño, 2014):

Problema de los tres colores

El Problema de los Tres Colores [Díaz, 2008], tiene como principal aplicación la coloración de países en un mapa. Es un caso típico en el etiquetado de grafos, que consiste en la asignación de etiquetas (colores) a los elementos del grafo. El objetivo de esta asignación, es que los vértices adyacentes de un grafo no compartan el mismo color, principio que se extiende a las aristas y caras del grafo en cuestión.

]]>

Este problema, se logra representar matemáticamente empleando enteros no negativos, que codifican la presencia de cada color en un determinado vértice. De forma general se puede emplear un conjunto finito como conjunto de colores. La naturaleza del problema depende del número de colores, y no de cuales sean estos. (Ver figura 2)

Redes de procesadores evolutivos

Las NEP, son modelos computacionales de optimización y búsqueda de soluciones inspirados en la biología celular. Estos modelos, son no deterministas y masivamente paralelos y pueden abordar la solución de problemas NP - Completos en tiempo polinomial y se enmarcan dentro de lo que se denomina Computación Natural. (Martínez, 2008) Se considera a la Computación Natural como una rama de la Inteligencia Artificial. En las NEP, las células son descritas por un conjunto de palabras, evolucionando producto de mutaciones, las cuales son representadas como operaciones sobre estas palabras, asemejándose a la manera en que este proceso es llevado a cabo en las cadenas de ADN. (Păun, 1998)

Al terminar el proceso de mutación, solo las células con cadenas correctas sobrevivirán. Estas cadenas serán las soluciones a los problemas. La principal fortaleza de estos modelos radica en la simultaneidad en la ejecución del proceso, para lo cual es necesaria una arquitectura en paralelo y distribuida que consiste de una serie de procesadores simples.

Los procesadores se ubican en los nodos de un grafo completo, los cuales son capaces de manipular datos asociados con el nodo correspondiente. Cada nodo opera sobre los datos locales con la posibilidad de realizar algún tipo de mutación puntual (inserción, borrado o sustitución de un símbolo), similar a la capacidad de las células para dividirse. Estos nodos actúan como un filtro, cuyo funcionamiento está definido por alguna regla, conocidas como Reglas de Evolución. Los datos locales son entonces enviados a través la red siguiendo los protocolos definidos. Solamente los datos que sean capaces de pasar el proceso de filtrado podrán ser comunicados. Adicionalmente, los datos en los nodos son organizados en forma de largos multiconjuntos de palabras donde cada una puede aparecer en un número arbitrariamente largo de copias y donde todas las copias son procesadas en paralelo para que cada posible acción se realice.( Batard, 2012)

Conceptos básicos sobre NEP

]]> Una Red de Procesadores Evolutivos de dimensión n se define como: ∑ = {V, N0, N1,…, Nn}. Donde V es un alfabeto y los procesadores Ni están conectados a grafo. Unacadena χ, de longitud m que pertenece al alfabeto V, es una secuencia de símbolos a1a2…am donde el símbolo ai Є V para todo 1≤ i ≤ m. El conjunto de todas las cadenas pertenecientes a V se denota por V* y la cadena vacía por ɛ. [Díaz, 2008] Si la misma regla de sustitución o eliminación puede reemplazar diferentes ocurrencias del mismo símbolo dentro de una cadena, todas estas ocurrencias deben ser reemplazadas dentro de las diferentes copias de esa cadena. El resultado es un multiconjunto en el cual cada cadena que puede ser obtenida aparezca en un número arbitrariamente largo de copias.

Para tal efecto, se define que el grafo es: G = ({1,2,…, n}, {e1, e2,…, em}) con et = {kt, lt}, 1≤ kt ≤ lt ≤ n, 1 ≤ t ≤ m. Se considera el alfabeto U = V U V’ U T U A, donde V = {b, r, g}, T= {a1, a2,…, an} y A= {A1, A2,…, An}.

Se construyen los siguientes procesadores de un NEP:

N0 = {{ a1, a2, …, an }, {ai → bAi,, ai → rAi , ai → gAi | 1 ≤ i ≤ n}, � 0, {Ai| 1 ≤ i ≤ n }}

En resumen, el procesador N0 genera todas las cadenas que codifican posibles combinaciones de color y posteriormente los procesadores Net1, Net2, Net3, Net4 filtran dichas cadenas en la arista et. La repetición de dicho proceso de filtrado para el resto de las aristas provoca la obtención de la solución al problema. Es decir, en cada paso evolutivo (filtro) se obtienen combinaciones de colores posibles soluciones al problema y al terminar todo el proceso evolutivo (paso por todos los filtros) es que se obtiene la solución final. (Castaño, 2014)

La arquitectura de la NEP que se define para el Problema de los Tres Colores, a partir del grafo G, es la siguiente:

Implementación

]]>

Para la implementación en Hardware (FPGA) de la Red de Procesadores Evolutivos para solucionar el problema antes mencionado, se deben tener en cuenta los siguientes elementos:

A partir de lo anterior, se propone el siguiente diagrama en bloques del sistema:

Bloque RAM_IN

A la memoria donde se guardan las combinaciones de colores generadas por N0 se le llama RAM_IN. El formato de estas combinaciones de colores, es el siguiente:

<color><NODO A> <color><NODO C> <color><NODO D> <color><NODO E> ]]>

Por tanto, una combinación de colores es: bAgCrDbE. En este caso el nodo A está coloreado en azul, el nodo C en verde, el D en rojo y el E en azul.

Para procesar estos datos en el FPGA, se codificaron los colores y los nodos con 2 bits cada uno. Esto provoca que las cadenas que codifican combinaciones de colores tengan 16 bits, 4 bits por cada combinación de <color><NODO>.

Los nodos fueron codificados de la siguiente manera:

00 - Nodo A, 01 - Nodo C, 10 - Nodo D y 11 - Nodo D.

Los colores se codificaron de la siguiente forma:

00 – Rojo, 01 – Verde, 10 - Azul y 11 - Sin color.

La combinación 11 representa el caso en que un nodo no está coloreado. Esto debe ser tenido en cuenta pues en muchas de las combinaciones de colores generadas por el procesador N0 no se le asignan colores a los nodos, sobre todo en las primeras, que es cuando empieza la asignación. (Castaño, 2014) ]]>

Estas combinaciones de colores que se ubican en la memoria pueden ser soluciones o no al problema. La NEP que se diseña, se encargará de filtrar cada una de ellas y determinar cuáles son soluciones al problema planteado. La memoria se implementa a partir de la descripción de su comportamiento en VHDL y tiene un tamaño de 8 Kb. Se ubica dentro del FPGA en uno de los bloques predefinidos para memorias de este tipo.

Bloque NEP

Para el proceso de filtrado se diseña el bloque macro “NEP”, que cuenta con 4 bloques internos. Cada uno de estos bloques está en función de una arista (et) del grafo del problema. En estos, es donde se implementan las reglas de evolución y se nombran NEP e1 (Net1), NEP e2 (Net2), NEP e3 (Net3) y NEP e4 (Net4). Internamente cada bloque de filtrado está formado por 4 procesadores evolutivos. Es decir, las combinaciones de colores deben ser analizadas por 16 procesadores evolutivos para determinar si son solución o no al problema.

La arquitectura de cada bloque de procesamiento (filtrado), implementados en VHDL a partir de la descripción de su estructura, se muestra a continuación.

En la figura anterior se puede apreciar la implementación de las reglas de evolución, donde A1 es la arista en análisis (et) y C1i y C1j son los colores de los nodos en los extremos de la arista. ]]>

El bloque de filtrado NEP e1 (Net1), es el encargado de recibir el dato procedente de la memoria RAM_IN. En este se valida la pertinencia de los datos asociados a los colores y los nodos de toda la combinación de colores. Si los datos anteriores son válidos y se cumplen las reglas de evolución para la arista et1, el dato pasa al bloque siguiente en su formato original. De lo contrario, lo que se transfiere es el valor “0000” hexadecimal, lo cual indica que la cadena recibida no es solución al problema. Lo anterior significa, que la célula no sobrevivió al proceso de mutación.

Los bloques NEP e2 (Net2) y NEP e3 (Net3) trabajan de igual forma, actuando sobre sus aristas et2 y et3 respectivamente. En ambos casos se recibe la combinación de colores procedente del bloque anterior, si se cumplen las reglas de evolución, el dato se transmite al siguiente. De lo contrario, también se transmite el dato “0000” hexadecimal.

Al final, el bloque NEP e4 (Net4) recibe la cadena procedente de NEP e3 (Net3) para filtrar la arista et4. Si se cumplen las reglas de evolución, entonces la combinación de colores recibida es solución al problema, por ser este el último paso evolutivo. Se procede entonces a enviar el dato para su almacenamiento en la memoria RAM_OUT y se habilita la escritura (WE) en dicha memoria. Si el dato no cumpliera con las reglas, no se guarda nada en RAM_OUT.

En este diseño, la secuencia del procesamiento de las combinaciones de colores entre los bloques de filtrado se realiza de forma serie. Esto se debe a que cada bloque solo puede comprobar el cumplimiento de las reglas de evolución de su arista (et) cuando le llega el dato desde el bloque anterior. Sin embargo, el procesamiento interno de cada bloque de filtrado es en paralelo, pues la salida toma valores según la concurrencia con que cambie la entrada. Esto último es producto de las ventajas que ofrecen los FPGA.

Bloque RAM_OUT

]]>

Este bloque corresponde a la memoria donde se guardan las combinaciones de colores generadas por el procesador N0 que cumplen con todas las reglas de evolución, es decir, las soluciones al problema. Esta memoria es igual a RAM_IN, la cual se implementa a partir de la descripción de su comportamiento en VHDL y tiene un tamaño de 8 Kb. También se ubica dentro del FPGA en uno de los bloques predefinidos para memorias de este tipo.

En la tabla siguiente se muestran las 12 posibles soluciones al Problema de los Tres Colores, a partir del grafo G. Esto es lo que debe contener la memoria RAM_OUT al terminar el proceso de filtrado.

RESULTADOS Y DISCUSIÓN

Síntesis, Implementación y Simulación

De la síntesis del diseño, se obtiene el esquema eléctrico de la Implementación de la NEP sobre el FPGA, la cual se muestra a continuación. Se identifican claramente los componentes NEP e1, NEP e2, NEP e3, NEP e4, RAM_IN y RAM_OUT. Nótese la similitud de este esquema eléctrico con el diagrama en bloques presentado anteriormente. (Ver figura 7)

Luego de la implementación del sistema, se obtuvo el siguiente resumen de la utilización de los componentes internos del FPGA. Los datos demuestran que este algoritmo complejo fue implementado utilizando muy pocos recursos de la FPGA, lo cual demuestra la factibilidad de la solución. (Ver tabla 2)

]]> La simulación del sistema arrojó el resultado que se muestra a continuación. Se visualizan varias señales:Los valores de las señales “salida_mp “y “salida” tienen al inicio de la simulación estados indeterminados (color naranja). Esto se debe a que el acceso a las memorias se hace secuencial, y mientras que por sus entradas de reloj no llegue un flanco de reloj, no habrá nada que mostrar.

Los valores de las 12 soluciones al problema, en la simulación, se encuentran en hexadecimal para simplificar el tamaño de la imagen y facilitar su entendimiento. Las combinaciones asociadas a estos datos hexadecimales pueden ser consultadas en la tabla 1.

Herramientas y Dispositivos ]]>

La herramienta de software que fue utilizada para la programación, síntesis, implementación y simulación del sistema es el entorno de diseño ISE 12.1 (Entorno de Software Integrado). Este proporciona un conjunto integrado de herramientas para la implementación de sistemas sobre FPGA, producidos por la compañía Xilinx. (Xilinx, 2015)

El flujo de diseño con ISE es el siguiente: (Castaño, 2014)

El sistema fue probado en el Kit de Desarrollo Atlys Board de Digilent. Contiene un FPGA Spartan-6 LX45 de Xilinx y otras múltiples funcionalidades. (Digilent, 2014) La programación del FPGA de dicho Kit, se realizó vía USB.

Los kits de desarrollo son plataformas de hardware que permiten la implementación práctica de sistemas digitales. Con ellos se puede comprobar el funcionamiento real de los diseños, previamente simulados. Ofrecen múltiples ventajas, como que no se necesita fabricar placas de circuito impreso, la misma placa se puede reutilizar en múltiples aplicaciones y permite el desarrollo rápido de prototipos. (Ramírez, 2011)El FPGA del Kit está desarrollada sobre tecnología de 90nm, con una capacidad de hasta 376 pines de E/S simples ó 156 pares de E/S diferenciales. La estructura interna de esta familia está conformada por Bloques de E/S (IOB, Input Output Block), Bloques Lógicos Configurables (CLB, Configurable Logic Blocks), Manejador de Reloj Digital (DCM, Digital Clock Manager) y Ram de Bloque (BRAM, Block Ram). (Xilinx, 2015)

]]>CONCLUSIONES

Las Redes de Procesadores Evolutivos son propicias para la solución de problemas NP – Completos, como el de los Tres Colores. Luego de la realización este trabajo, se obtuvieron las siguientes conclusiones:

Todo lo anterior demuestra la viabilidad de la implementación de las NEP en dispositivos de hardware.

REFERENCIAS BIBLIOGRÁFICAS ]]>

Ashenden, Peter J. The VHDL Cookbook. Departamento de Ciencias de la Computación, Universidad de Adelaide, Australia. Julio, 1990.

Batard Lorenzo, David & Martínez Hernando, Víctor J. “Simulación de NEP en Java”, Evento UCIENCIA 2012, La Habana, Cuba, 2012.

Implementación sobre FPGA de una Red de Procesadores Evolutivos (NEP) para solucionar el Problema de los Tres Colores. I Convención Internacional de Ciencias Técnicas y VII

Conferencia Internacional de Ingeniería Eléctrica, Universidad de Oriente, Santiago de Cuba, Cuba, junio 2014. ISBN: 978-959-207-529-0

Implementación en Hardware Reconfigurable de una Red de Procesadores Evolutivos para la Solución a un Problema NP-Completo. I Conferencia Internacional UCIENCIA, Universidad de las Ciencias Informáticas, La Habana, Cuba, abril 2014. ISBN 978-959-286-026-1

]]>

Díaz Martínez, Miguel Ángel. “Redes de Procesadores Evolutivos con Filtros en las Conexiones”. Tesis Doctoral, Universidad Politécnica de Madrid, España, 2008.

Digilent. Información obtenida en fecha 26 de junio de 2014. Información en http://www.digilentinc.com/Products/ATLYS.

Freire Rubio, Miguel Ángel. “Manual de Introducción al lenguaje VHDL”. Universidad Politécnica de Madrid, España. Año 2011.

Martínez Hernando, Víctor. “Desarrollo de Sistemas Físicos para Implantar Modelos de Computación con Membranas”. Tesis Doctoral, Universidad Politécnica de Madrid, España (2008).

Păun, Gh., Rozenberg, G., & Salomaa, A., “DNA Computing. New Computing Paradigms”, Berlin, Springer, 1998.

]]>

Ramírez Despaine, Maikel. “Controlador Lógico Programable basado en Hardware Reconfigurable”. Tesis de Maestría, CUJAE, La Habana, Cuba, 2011.

Xilinx. Información obtenida en //www.Xilinx.com. Información Publicada el 20 de febrero de 2013, consultada el 15 de mayo de 2015.

Recibido: 30/07/2015

Aceptado: 15/10/2015