Mi SciELO

Servicios Personalizados

Articulo

Indicadores

-

Citado por SciELO

Citado por SciELO

Links relacionados

-

Similares en

SciELO

Similares en

SciELO

Compartir

Ingeniería Electrónica, Automática y Comunicaciones

versión On-line ISSN 1815-5928

EAC vol.34 no.2 La Habana mayo-ago. 2013

ARTICULO ORIGINAL

Diseño en VHDL de un controlador HDLC.

Desing in VHDL of HDLC controller.

Ilena Del Valle Crespo1, Dallán Torres Dávila2, Yudith Florencia González Padilla3, Javier González Badillo3, Yosbel J. Herrera Fonseca3, Juan C. Molina Campos3.

1 Centro de Investigación y Desarrollo Técnico «CIDT», Cuba, cidt@mn.mn.co.cu

2 ETECSA, Cuba

3 Instituto Superior Politécnico José Antonio Echeverría,Cuaje, La Habana, Cuba, florencia.gp@electrica.cujae.edu.cu

RESUMEN

En esta investigación se presenta el diseño de un módulo de hardware embebido con la funcionalidad de un controlador HDLC (de sus siglas en inglés High Level Dato Link Control) para una interfaz de línea digital E1. El sistema diseñado realiza las tareas de un transmisor-receptor, encargándose de acciones como la inserción y detección de las banderas de inicio y fin de trama, la inserción y detección de ceros para evitar la existencia de la secuencia de bandera en el campo de dato y el chequeo de trama. También incorpora una interfaz con un microprocesador para la configuración de los parámetros iníciales y a través de ella se adquieren los datos de control que se van a transmitir o recibir. Cada uno de los bloques presentes en el sistema se ha diseñado a través del lenguaje de descripción de hardware VHDL (de sus siglas en inglés Very High Density Language) empleando el software Xilinx ISE Design Suite 12.4. Finalmente, la investigación es implementada en la tarjeta de desarrollo SPARTAN3 Starter Board Kit y los resultados quedan validados con las comprobaciones pertinentes.

Palabras claves: controlador HDLC, trama, VHDL, FPGA, xilinx.

ABSTRACT

This research presents the design of an embedded hardware module with functionality of a HDLC controller to an E1digital line interface. The designed system performs the tasks of a transmitter-receiver, responsible for actions such as insertion and detection of start and end flags of frame, the insertion and detection of zeros to avoid the existence of the sequence of flags in the data field and the frame check. It also incorporates an interface with a microprocessor for setting the initial parameters and through it control data's are acquired to be transmitted or received. Each of the blocks in the system has been designed through the hardware description language VHDL using Xilinx software ISE Design Suite 12.4. Finally, research is carried through in the development board Spartan3 Starter Board Kit and the results are validated with the appropriate verifications.

Key words: frame, HDLC controller, VHDL, FPGA, xilinx.

INTRODUCCION

El protocolo HDLC maneja una estructura orientado a bitpacket switching protocol defined in the X.25 (Level 2) recommendations of the . Este se encuentra ubicado en la capa de enlace del modelo OSI y es responsable de la transferencia fiable de información a través de un circuito de transmisión de datos digital a 2048KHz; recibe peticiones de la capa de red y utiliza los servicios de la capa física. Entre sus funciones están el control de errores, de flujo y la inicialización y desconexión de estaciones1. El protocolo se define en la norma ISO/IEC 13239:2002(E)

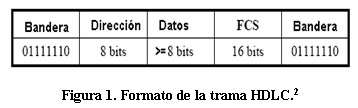

en la cual se especifica un formato de encapsulamiento de trama para enlaces de datos sincrónicos y orientados a la conexión el cual se presenta en la figura 1.

La trama del protocolo está constituida por un campo de bandera de ocho bits el cual da inicio y fin de trama; además tiene un campo de dirección que consta de un byte que identifica al módulo; le sigue el campo de control que es de longitud extendida ya que puede ser de uno o más bytes; después se tiene en 16 bits una secuencia de verificación de trama (FCS).

Esta investigación se enfocó en diseñar un sistema con funcionalidad semejante al controlador de la familia MT8952B, el cual utiliza una de las versiones del protocolo HDLC como resultado de su estandarización, como es el LAPB (de sus siglas en inglés Link Access Procedure Balanced). Su función es el procedimiento de acceso al enlace balanceado usado en las interfaces X.25, nivel 2, procurando una entrega segura de los datos entre el dispositivo del usuario y la red de paquetes.

En la actualidad se encuentran FPGA de alto rendimiento con sistemas de millones de compuertas y bloques embebidos de microprocesadores, interfaces de entrada/salida de muy alta velocidad (pudiendo sobrepasar los 5Gbps).Lo anterior justifica que estos dispositivos sean aptos para casi cualquier aplicación, como por ejemplo sistemas de comunicaciones, redes neuronales artificiales y procesamiento digital de señales, por mencionar algunos.

El éxito que han tenido los FPGA se debe en gran medida al hecho de que, a pesar de sus vastos recursos, su valor comercial no se ha incrementado en la misma proporción que estos3. Por ello muchos sectores del país se han acogido a la modernización de sus dispositivos haciendo uso de módulos de hardware embebido (HE), que no es más que descripciones software de componentes hardware que implementados en un FPGA como un módulo de propiedad intelectual (IP), pueden sustituir la circuitería instalada y obsoleta, con ventajas tales como: la reducción en los costos y la capacidad de reutilización, permitiendo esto el aprovechamiento de las capacidades tecnológicas existentes.

DISEÑO DE LOS BLOQUES FUNCIONALES DEL CONTROLADOR HDLC.

En esta seccion se presentará el diseño de los diferentes bloques que conforman el módulo de hardware embebido que será implementado en el FPGA, con la funcionalidad de controlador HDLC para una interfaz digital de flujo E1. Con el uso de la herramienta de diseño ISE 12.4 del fabricante Xilinx, se construyeron los bloques que conforman los subsistemas, los cuales obedecen a los requerimientos del controlador de la familia MT8952B.

Descripción general del diseño del controlador HDLC.

En un sentido el sistema adquiere el dato que da el microprocesador a través del buffer de transmisión para incorporarlo en el intervalo de tiempo del canal 16, o en cualquier otro intervalo de tiempo de canal que sea elegido por el modo externo, a través de la salida ST_BUS; y en el otro sentido se adquiere el dato a través de la señal ST_BUS_RX para enviársela al microprocesador a través del buffer de recepción y este pueda procesarla. Ambos sentidos cuentan con el suministro de reloj y señales que le permitan mantenerse sincronizado con el flujo E1 y además, una interfaz con el microprocesador que permite el intercambio necesario de información. Para poder lograr toda la funcionalidad que respecta al controlador HDLC, el diseño quedó divido en 5 subsistemas como se muestra en la figura 2.

· Subsistema Interfaz con el Microprocesador: Diseñado con el propósito de comunicar al controlador HDLC con el microprocesador. Con el objetivo principal de configurar el modo de trabajo del controlador y escribir o los datos a entramar o leer los que se reciben .

· Subsistema de Control: Encargado de actualizar todos los registros que conforman la interfaz con el microprocesador.Informa al Subsistema de Transmisón sobre el estado delos buffer de transmisión y recepción, así como del estado delos byte a transmitir y recibir.

· Subsistema de Temporización: Garantiza que el dato sea transmitido o recibido en el momento adecuado, ya sea en el intervalo de tiempo de canal 16 de la trama E1 o en cualquier otro intervalo de tiempo de canal seleccionado por el microprocesador a través de la temporización externa.

· Subsistema de Transmisión: Conforma la trama HDLC siguiendo los procedimientos de la norma IS13239. Le agrega al dato suministrado por el microprocesador, los campos de FCS y las banderas de inicio y fin.

· Subsistema de Recepción: Una vez recibida la trama, permite el desencapsulamiento del dato siguiendo los procedimientos de la norma IS13239. A través de los diferentes bloques que lo conforman es capaz de extraer el dato de la trama y entregarlo a la interfaz con el microprocesador.

Entradas y Salidas generales del Controlador HDLC.

Según como se presentó en la figura 2 el sistema está compuesto por un número de señalesde entrada y salida las cuales se describirán en este epígrafe.

D_in: A través de esta señal el microprocesador envía los datos pertenecientes a los registros o los datos propios de control que conforman la trama HDLC.

D_out: A través de esta señal el microprocesador recibe los datos provenientes de los registros o los datos propios de control que conforman la trama que se recibió.

A31...A0: Estos bits constituyen el bus de direcciones, que posibilita que el microprocesador direccione el controlador HDLC, así como un registro en particular.

R_W: Bit que indica si el microprocesador va a realizar una escritura o una lectura. Si se encuentra en nivel alto indica que se realizará una lectura(R) y si se encuentra en nivel bajo se realizará una escritura (W).

EN: Bit que habilita, de encontrarse en nivel alto, el bus de direcciones, las funciones de lectura y escritura, así como la transferencia de datos hacia el bus de datos.

CS: De encontrarse este bit en nivel alto, habilita las operaciones de lectura y escritura hacia los registros del controlador.

IRQ: Señal de un bit que solicita interrupción al microprocesador, para esto debe pasar a nivel bajo.

CLK: Entrada de reloj del sistema con un valor de 2048KHz.

rst: Inicializa todos los bloques que comprenden este controlador, cuando se encuentra en nivel bajo.

F0: Señal de un bit que cuando sube su nivel a `1', indica que se comenzó a transmitir el canal 0 de la Trama E1. Está dirigida al Subsistema de Temporización para lograr el modo interno de temporización.

TX_CEN: Señal que actúa directamente sobre el Subsistema de Temporización permitiendo el modo externo; cuando la transmisión está concebida por esta señal no necesariamente el dato de control va en el canal 16 de la Trama E1, se transmite en el canal que ella seleccione.

RX_CEN: Señal que actúa directamente sobre el Subsistema de Temporización permitiendo el modo externo; cuando la recepción está concebida por esta señal no necesariamente el dato de control va a recibirse en el canal 16 como está preestablecido.

ST_BUS: Señal de 8 bit, que permite que el módulo HDLC envié la trama de control hacia el transceptor y así incorporarla al flujo digital E1.

ST_BUS_RX: Señal de 8 bits, a través de la cual se obtiene el dato de control proveniente del transceptor del flujo digital E1.

TEOP: Señal de un bit, que sube su nivel a uno para indicar fin de transmisión del espacio de dato de la trama de control.

REOP: Señal de un bit, que sube su nivel a uno para indicar fin de recepción del espacio de dato de la trama de control.

Subsistema Interfaz con el Microprocesador

El subsistema Interfaz con el Microprocesador es el encargado de comunicar el módulo del controlador HDLC con el microprocesador. Para poder realizar la comunicación, el microprocesador debe habilitar el módulo del Controlador HDLC a través de la señal ENen nivel alto, realizar la selección del módulo a través de la señal CS en `1' y el bit más significativo del bus de direcciones en nivel alto (A(31)= `1'). Una vez que se habilitó la comunicación hacia el módulo del controlador, si lo que se desea realizar es una escritura, la señal R_Wdebe bajar su nivel a cero, se escribe el dato en el bus de ocho bits D_inque entra al módulo y se direcciona a través de los tres bits menos significativos del bus de direcciones (A(2..0)) a cual de los tres registros de escritura se le desea enviar el dato o si es hacia el Buffer FIFO(Primero que entra, primero que sale, de sus siglas en inglés) de Transmisión. Si lo que se desea realizar es una lectura, la señal R_W debe subir a `1', y se direcciona con los tres bits menos significativos del bus de dirección (A(2..0)) cual de los tres registros o Buffer FIFO de Recepción quiere ser leido por el microprocesador. Ambos procesos quedan esquematizados para una mejor comprensión en la figura 3.

Subsistema de Temporización

El Subsistema de Temporización es el encargado de que los datos se transmitan y reciban en el momento adecuado, ya que el bus de datos es compartido. Este subsistema permite que el controlador pueda trabajar en modo de temporización interno o externo.

En el modo interno los datos del canal de señalización se encuentran en el intervalo de tiempo del canal 16 de la trama E1 y se utilizan las señales F0 y CLK para su transmisión o recepción. En el modo externo los datos del canal de señalización se encuentran en el intervalo de tiempo seleccionado desde el exterior, por lo que se utilizan en este caso las señales TX_CEN y RX_CEN.

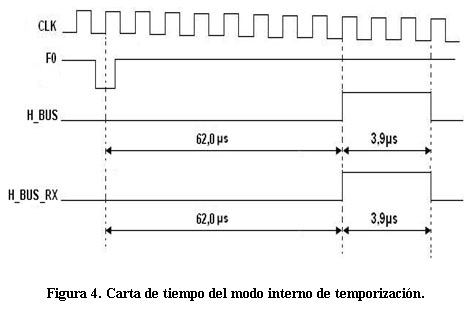

A continuación en la figura 4 se presenta la carta de tiempo referente al modo interno de temporización, así como los tiempos a esperar por el contador de pulsos del reloj para obtener el intervalo de tiempo del canal 16 de la trama E1, para el proceso de transmisión y de recepción. Una vez que la señal F0baja su nivel a cero, se espera un tiempo de 62,0µshasta un período de reloj antes de que comience el canal 16. En este caso se pierde un periodo del reloj debido a la existencia de un Multiplexor de Temporización antes del Subsistema de Transmisión o de Recepción. Una vez concluido el tiempo de 62,0µs, las señales H_BUS o H_BUS_RX suben su nivel a uno durante 3,9µs para habilitar la transmisión o la recepción según corresponda, durante el tiempo que demora el canal 16 de la trama E1.

Subsistema de Transmisión

Para el diseño del Subsistema de Transmisión se realizó un estudio detallado de las características de una trama HDLC, partiendo de este, el subsistema quedó diseñado como un conjunto de tres bloques.

Para realizar el proceso de transmisión, el microprocesador debe inicializar todo el sistema, es decir fijar los parámetros de habilitación de la transmisión a través de TX_EN y el modo de temporización deseado con la señal IC. Este a su vez es el encargado de proveer los datos de control que se almacenarán en el buffer tipo FIFO que se encuentra en la Interfaz con el Microprocesador. Posteriormente, el canal de transmisión tomará los datos del buffer tipo FIFO, los encapsula y los envía por el bus de salida en el tiempo del canal de señalización habilitado por el Subsistema de Temporización con la señal H_BUS. Este canal, de encontrar vacío el almacenador de datos, transmitirá cualquiera de los tres posibles estados inactivos (banderas continuas, inactivo (FFh), o go_ahead (7Fh)), el cual será previamente seleccionado por el microprocesador a través del Registro de Control. Si es habilitado el modo transparente se inhabilitará entonces el protocolo HDLC y los datos se transmitirán tal y como se escriben en el Buffer FIFOde Transmisión. Si el buffer contiene datos y no está habilitado el modo transparente, entonces los datos pasarán por el canal de transmisión con el objetivo de ser entramados y posteriormente transmitidos. Una vez que se comienzan a transmitir los datos entramados, el microprocesador puede decidir abortar la trama, por lo que se transmitirá la secuencia de aborto «11111111» , se limpiará el registro que lleva el computo de la secuencia de FCS y posteriormente se comenzará a transmitir una nueva trama, comenzando por su bandera de inicio. En la figura 5 se muestra el algoritmo antes descrito lo que permite una mejor comprensión.

Subsistema de Recepción

Para realizar el diseño del canal de recepción se tuvo en cuenta el estudio del formato de trama del protocolo HDLC, así como el diseño final del canal de transmisión y los requisitos del hardware.

Para este proceso de recepción también se necesita que el microprocesador inicialice los parámetros para la recepción con RX_EN y con RX_AD, habilitarla verificación o no de la dirección en el primer byte de dato, así como seleccionar el modo de temporización a través de IC. Una vez habilitado el bus de entrada ST_BUS_RX por el Subsistema de Temporización con la señal H_BUS_RX, se reciben los datos en modo serie que pueden corresponder con: la secuencia de cualquiera de los tres posibles estados inactivos, según el que esté seleccionado por el microprocesador a través del Registro de Control. Si la secuencia indica estado transparente, entonces se deshabilitará el protocolo HDLC y los datos que se reciban se escriben directamente en el Buffer FIFO de Recepción que se encuentra en la Interfaz con el Microprocesador. De no estar habilitado este modo, si se detecta una bandera y posteriormente un byte de secuencia desconocida, este se pasará al interior del canal de recepción para desencapsular el campo de dato y almacenarlo en el buffer. Una vez que se comience a recibir datos después de la bandera de inicio, se verificará que este no coincida con la secuencia de aborto de trama «11111111», ya que de ser así se limpia el registro que almacena el cómputo de la secuencia de FCS y se pasa a detectar la bandera de inicio de una nueva trama. Si el número de datos entre la bandera de inicio y de fin es menor que cuatro byte, estos datos no se almacenarán en el buffer, ya que corresponden a una trama invalida (una trama válida debe tener entre las bandera de inicio y fin cuatro o más bytes). En la figura 6 se muestra un esquema con el algoritmo de trabajo, el cual facilitará su comprensión.

IMPLEMENTACIÓN DE LOS BLOQUES FUNCIONALES EN EL FPGA

En esta sección se describen los resultados obtenidos de la implementación de la entidad VHDL de más alto nivel del controlador HDLC diseñado.

Inicialmente la herramienta de diseño ISE, permitió con la síntesis de los subsistemas de manera individual, chequear la sintaxis de todos los bloques que los conforman, así como obtener simulaciones a nivel funcional donde no se tienen en cuenta los retardos provocados por el hardware. En este caso se utilizan los modelos de Test Bench que brinda la herramienta, donde se fija el estado de las entradas de cada subsistema según lo estime el programador.

Una vez realizada la síntesis de todos los subsistemas, se sintetizó la entidad VHDL de más alto nivel, que permite en un futuro la implementación del controlador en el FPGA. Se obtuvo con ella datos referentes al consumo de recursos del FPGA, dicha tabla se muestra en la figura 7.

Como se observa en la figura 7, se utilizó el 31% de los LUTs (de sus siglas en inglés, Look-Up Tables) disponibles en el FPGA, que corresponden a 1195 LUTs. Además, para los registros generados en la descripción VHDL de los módulos, se utilizó el 18% del total, lo que equivale a 706 flip-flops. Se utilizó el 18% de los bloques de entrada/salida para las conexiones externas del FPGA y los Slices consumidos representaron el 34% de los existentes.

Una vez realizada la síntesis general del sistema HDLC, se quiere con el uso de la herramienta Platform Studio, desarrollar un módulo IP que contenga el hardware HDLC diseñado. Este periférico se instanció en un sistema empotrado a través del bus PLB para realizarle una interfaz con el procesador Microbleaze. Posteriormente se implementó una aplicación software de ejemplo, a través de la cual se comprobó el correcto funcionamiento del módulo HDLC.

Luego de implementar el diseño, se crea un fichero para programar el FPGA. Este fichero se llama bitstream y es el archivo del sistema con extensión .bit que puede ser descargado directamente en el FPGA.

La tarjeta de desarrollo utilizada, incorpora en su estructura el FPGA Spartan3 XC3S400-FT256. Este dispositivo brinda al usuario gran rendimiento y abundantes recursos lógicos, ya que contiene internamente 400 000 compuertas, 8064 celdas lógicas, 898 CLBs (de sus siglas en inglés Configurable Logic Blocks), 56 kbits de memoria distribuida y 288 Kbits de bloques de RAM. También posee un puerto JTAG (de sus siglas en inglés Joint Test ActionGroup) que se usa para enviar la configuración hacia el FPGA directamente desde una PC a través del puerto paralelo. De esta forma es que se logra descargar el programa confeccionado en el FPGA e iniciar las mediciones y comprobación de los resultados reales.4

Para validar el correcto funcionamiento del controlador HDLC, se hizo necesario el uso del hardware el cual se está sustituyendo, para adquirir de él el reloj de 2MHz del sistema y la señal FO. Se hizo también uso de un osciloscopio digital.

Implementación del Subsistema Interfaz con el Microprocesador

Primeramente se le realizan las pruebas a la Interfaz con el Microprocesador, ya que chequeando su correcto funcionamiento, se asegura la comunicación del módulo HDLC con el Microprocesador.

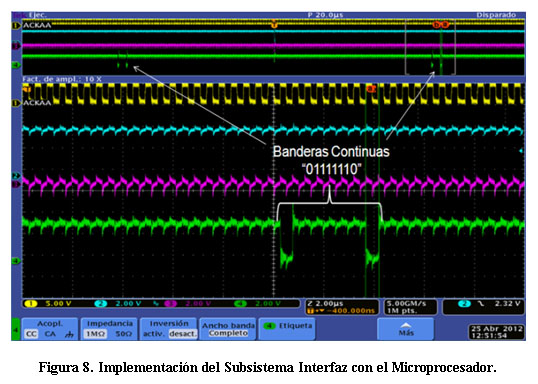

Para llevar a cabo esta prueba se direccionó y se escribió en el Registro de Control, habilitando así la transmisión, el modo interno de temporización y el estado inactivo de banderas continuas, a través de la secuencia «10010100». En la figura 8 se muestra la transmisión del estado inactivo de banderas continuas.

Implementación del Subsistema de Temporización

Para evidenciar un correcto funcionamiento de este subsistema se hizo necesario el uso del osciloscopio, el cual permite observar las señales, su sincronismo con el reloj de 2,048MHz que se adquiere del hardware que quiere ser sustituido y los respectivos tiempos de demora.

Esta prueba fue hecha para el modo interno de temporización (IC= `1') del canal de transmisión. En la figura 9 se muestra la señal H_BUS que corresponde con la señal de color morado, la cual se encuentra en `1' pasado 62,0µs, después de que F0 (señal de color azul) baja su nivel a `0' y H_BUS mantiene su estado en `1' durante 3,9µs, el tiempo exacto del intervalo de tiempo del canal 16, todas estas señales sincronizadas con el reloj de 2,048 MHz (señalizado con color amarillo).

Implementación del Subsistema de Transmisión

Para poder llevar a cabo la transmisión, el microprocesador debe habilitarla inicialmente, así como establecer el modo de temporización y el modo de trabajo cuando el transmisor se encuentra en estado inactivo, configuraciones que se realizan a través de la Interfaz con el Microprocesador. El reloj del sistema y la señal FO se adquieren del hardware en desarrollo. En el bus de salida el dato de control se debe obtener con el formato de trama específico y debe ser en el momento del canal 16 de la trama E1, aspecto de gran importancia que se garantiza por el Subsistema de Temporización, a través de la señal H_BUS en `1'. Para poder realizar pruebas que validen la ocurrencia de una correcta transmisión se hizo el uso de un osciloscopio digital el cual permite observar el comportamiento de dicho proceso.

En la figura 10 se puede comprobar la correcta transmisión del dato en el formato de trama del protocolo HDLC. El dato del bus de salida (señal de color verde) garantiza la transmisión de una bandera de inicio de trama, dos datos de control los cuales coinciden con los que les fueron escritos por el microprocesador, la secuencia de corrección de errores de 16 bits correspondiente a este dato y por último la bandera de fin de trama. Para verificar que el dato se encuentra en el bus de salida en el momento oportuno se muestra también la señal de habilitación del bus, que brinda el Subsistema de Temporización (H_BUS, señalizada con el color morado).

Implementación del Subsistema de Recepción

Al igual que el proceso de transmisión, la recepción debe ser habilitada por el microprocesador, así como la selección del modo de temporización, y habilitar o no la detección de dirección en el primer byte del campo de dato de la trama. En esta prueba se adquiere el dato por el bus de entrada ST_BUS_RX, que llega desde el controlador de la familia MT8952B que se encuentra en la tarjeta que se quiere sustituir.

Para poder llevar a cabo esta prueba el procesador Microbleaze debe direccionar el Buffer FIFO de Recepción y habilitar la lectura de este, para que el dato salga por el bus de salida del módulo HDLC. Debido a que este procesador tiene un reloj de 50MHz no se sincroniza con el sistema diseñado, que trabaja con un reloj de 2MHz y se vio afectado la comprobación del proceso de recepción el cual es sensible a las demoras que se producen en la transición de los datos del Buffer de Recepción al Multiplexor, ya que el dato no se encuentra a la salida del módulo en el momento que el procesador realiza la lectura sino tres períodos del reloj de 2MHz después de habilitarla, lo que equivale a 75 períodos de reloj de 50MHz.

CONCLUSIONES

El presente trabajo estuvo orientado a la realización del diseño en VHDL de un controlador HDLC el cual fuera capaz de controlar el enlace de una interfaz de línea digital E1 y su implementación en un FPGA. El formato de trama de este protocolo se encuentra estandarizado en la norma IS12392 de la ISO y presenta mecanismos para no perder la sincronización frente a diversas situaciones que se den en el enlace. El mínimo número de datos que debe tener una trama para que sea válida es 2 byte, y se envía una secuencia de ocho unos consecutivos si el sistema quiere abortar la trama que se transmite.

Mediante la utilización de las herramientas de diseño ISE Design Suite 12.4de Xilinx y el Spartan3 StarterBoard Kit, quedó confeccionado el módulo de transmisión y recepción de los datos de control, así como realizar todo el procesamiento necesario para el funcionamiento interno.

Se diseñó una interfaz con un microprocesador que se encarga de habilitar el canal de transmisión y recepción de los datos de control, el tipo de interrupción, decidir el modo de temporización, así como registrar el estado interno del sistema. Para su validación se integró al sistema un Microblaze a través de un bus PLB. Se desarrolló también un número de pruebas las cuales dieron validez al Subsistema de Control encargado este de actualizar al microprocesador del estado de los buffer de transmisión y recepción, el tipo de interrupción ocurrida, así como controlar el canal de transmisión.

Se verificó, en la práctica, el potencial que poseen los FPGAs actuales y, en particular, la arquitectura de los FPGA de la familia Spartan3, cuyos componentes han facilitado la descripción VHDL e implementación de funciones de gran complejidad de cómputo.

Los IP Cores que se encuentran disponibles en la herramienta de desarrollo del Xilinx ISE Design Suite 12.4, constituyeron un importante apoyo en el diseño del proyecto, ya que con éstos, se llevó a cabo el diseño del Buffer FIFO de Trasmisión y de Recepción optimizando así recursos del FPGA.

Se verificó, en la práctica, el potencial que poseen los FPGAs actuales y, en particular, la arquitectura de los FPGA de la familia Spartan3, cuyos componentes han facilitado la descripción VHDL e implementación de funciones de gran complejidad de cómputo.

La propuesta de diseño contribuye al desarrollo tecnológico y sustituye elementos circuítales obsoletos por la puesta en marcha de tecnologías más avanzadas para la transmisión de datos.

REFERENCIAS

1. Comunicaciones, C.D., «Ejercicios Resueltos del Protocolo HDLC», Ingeniería en Sistemas de Información. Facultad Tecnológica Regional Santa Fe: Bogotá, Colombia, 2005.

2. ISO, «ISO/IEC 13239, Information technology: Telecommunications and information exchange between systems, High-level data link control (HDLC) procedures», I.O.f. Standardization, Edito, ISO/IEC: Suiza, p.140, 2002.

3. Leyva Hernández, G., «Generación de módulos aritméticos en punto flotante para procesamiento digital de altas prestaciones», Universidad de Guadalajara. Centro Universitario de Ciencias Exactas e Ingenierías: México DF, 2010.

4. Anaya, M. and A. Medina, «Diseño en VHDL de un transceptor de flujo E1 y su implementación en un FPGA», Departamento de Telecomunicaciones y Telemática, ISPJAE: La Habana. p.99, 2011.

Recibido: Abril 2013

Aprobado: Mayo 2013