Meu SciELO

Serviços Personalizados

Journal

Artigo

Indicadores

-

Citado por SciELO

Citado por SciELO

Links relacionados

-

Similares em

SciELO

Similares em

SciELO

Compartilhar

Ingeniería Electrónica, Automática y Comunicaciones

versão On-line ISSN 1815-5928

EAC vol.36 no.3 La Habana set.-dez. 2015

ARTÍCULO ORIGINAL

Límites impuestos por los elementos pasivos en el diseño de amplificadores de bajo ruido en tecnología CMOS

Constraints imposed by passive elements in the design of CMOS low-noise amplifiers

Msc. Jorge Luís González Ríos,I Dr. C. Robson Luiz Moreno,II Dr. C. Diego VázquezIII

I Centro de Investigaciones en Microelectrónica (CIME-CUJAE), La Habana, Cuba

II Universidade Federal de Itajubá (UNIFEI), Itajubá, Brasil

III Instituto de Microelectrónica de Sevilla (IMSE-CNM-CSIC), Sevilla, España

RESUMEN

En este trabajo se analizan las restricciones impuestas por los límites tecnológicos de los elementos pasivos en el diseño de un amplificador de bajo ruido (LNA) integrado en tecnología CMOS, de configuración fuente común con degeneración inductiva. A partir del análisis del circuito se establecieron dependencias cualitativas entre los valores de los elementos pasivos y los objetivos de síntesis del LNA (ganancia, corriente de polarización y ancho de los transistores), que permiten prever cómo los parámetros constructivos limitan el desempeño funcional. Estas dependencias fueron comprobadas y enriquecidas a través de simulaciones, realizadas para una tecnología CMOS de 130 nm con 1.2 V de alimentación y una frecuencia de trabajo de 2.45 GHz. Para la topología estudiada, se muestra que la ganancia máxima, la corriente de polarización mínima (y, por tanto, el consumo de potencia mínimo) y las dimensiones de los transistores que pueden ser utilizados en el diseño están determinadas por los valores extremos de inductancia y capacidad disponibles en el proceso tecnológico. Los resultados obtenidos corroboran la necesidad de incluir toda la información tecnológica posible de los elementos pasivos dentro del flujo de diseño de circuitos integrados para aplicaciones de radiofrecuencia.

Palabras claves: amplificador de bajo ruido (LNA), CMOS, circuito integrado, bajo consumo, elementos pasivos, radiofrecuencia (RF)

ABSTRACT

This paper analyses the impact of technological limits of passive elements on integrated CMOS Low-Noise Amplifiers (LNAs) design. The topology under study is the commonly used inductively degenerated common-source LNA. An equation-based analysis is presented, which is verified and complemented by means of simulation. Simulations were carried out using a 130-nm 1.2-V CMOS technology, working at 2.4 GHz. We obtained that inductance and capacitance values available in the technological process constraint the achievable maximum gain, minimum power consumption and transistor sizing. Results also show that designers must include as much information as possible about passive elements into the design procedure of radiofrequency integrated circuits. Key words: low-noise amplifier (LNA), CMOS, integrated circuit, low power, passive elements, radio frequency

INTRODUCCIÓN

En 1958, Jack Kilby demostró que era posible fabricar en una misma pieza de semiconductor los distintos componentes de un circuito, tanto los transistores como los elementos pasivos, dando origen al circuito integrado 1. Sobre la base de este hito, los avances que se sucedieron en la microelectrónica potenciaron el desarrollo vertiginoso de las tecnologías de las comunicaciones, la informática y las ciencias de la computación, imprescindibles en la sociedad moderna.

El mercado de fabricación de los circuitos integrados está ampliamente dominado por la tecnología CMOS, debido a que, entre otros factores, es la que presenta el menor costo de producción 2. La continua miniaturización de los transistores MOS ha permitido, además, aumentar la capacidad y velocidad de procesamiento de la información, con una disminución simultánea del consumo de potencia 3.

Esto ha beneficiado las prestaciones tanto de los circuitos digitales como las de los analógicos, incluyendo los de radiofrecuencia (RF) 4. La utilización de las actuales tecnologías CMOS submicrométricas permiten, por ejemplo, la integración en un mismo chip de circuitos de comunicación completos (desde los bloques de RF hasta el procesamiento digital en banda base) para la comunicación inalámbrica con frecuencias en el orden de los gigahertz (GHz) 5, 6. Sin embargo, y aun cuando los elementos pasivos estuvieron presentes desde la concepción de los circuitos integrados, la complejidad que presenta la fabricación y modelación de los mismos (principalmente de los inductores) es una de las causas que dificultan el diseño microelectrónico de RF7.

En los circuitos de comunicación integrados, el diseño de los bloques de RF constituye la dificultad fundamental para la implementación del sistema 8. En el caso particular de los receptores de RF, el rendimiento del amplificador de bajo ruido (LNA) es determinante en el desempeño del sistema como un todo 8, 9. Con el LNA se debe garantizar el mínimo nivel de señal detectable (sensibilidad), a través de un valor suficientemente alto de ganancia y una baja contribución de ruido 8-10. Simultáneamente, el LNA también debe ofrecer un valor adecuado de su impedancia de entrada (que garantice el acoplamiento de impedancias respecto a la salida de la etapa precedente, típicamente un filtro selector de banda con impedancia de salida de 50 Ω), un valor suficientemente alto de linealidad (caracterizada típicamente mediante el punto de intercepción de intermodulación de tercer orden, IP3 8) y un alto aislamiento inverso 10.

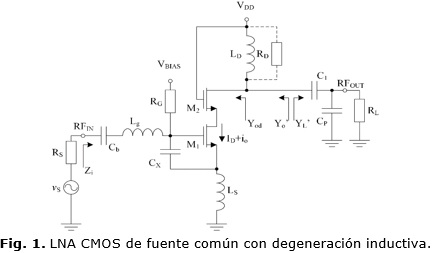

El LNA de configuración fuente común (CS-LNA) con degeneración inductiva (Fig. 1) es una topología ampliamente utilizada en los receptores CMOS integrados para comunicaciones inalámbricas de corto alcance (tales como WiFi, Bluetooth, y Zigbee) 9-11. En el diseño de un CS-LNA con ganancia y consumo de potencia determinados, los transistores pueden dimensionarse para minimizar la figura de ruido (NF), como ha sido demostrado en trabajos previos sobre esta topología 12-14. En el CS-LNA puede obtenerse alta linealidad con bajo consumo aprovechando un pico del IP3 que aparece en los transistores MOS polarizados en inversión moderada 15. Este pico del IP3 ocurre aproximadamente para un mismo valor de la densidad de corriente en el transistor de fuente común 16, 17, por lo que para un consumo determinado la linealidad pudiera maximizarse también a través del dimensionado apropiado de los transistores.

Según las consideraciones expuestas en el párrafo anterior, para balancear adecuadamente el ruido, la linealidad y el consumo de potencia del LNA se propone realizar una exploración del espacio de diseño, consistente en el barrido del ancho de M1 (W1) con distintos valores de la corriente de polarización (ID) 18. Para cada combinación de corriente y ancho de los transistores es necesario buscar las dimensiones de los elementos pasivos que garanticen los requerimientos de ganancia y acoplamiento de impedancias (síntesis del LNA), para luego obtener la figura de ruido y el IP3 de cada LNA sintetizado. El conjunto de resultados obtenidos para diferentes LNA conforman el espacio de diseño del cual se podrá escoger el circuito que será implementado. Sin embargo, la selección de los elementos pasivos en la síntesis de cada LNA están limitadas por las características tecnológicas de cada proceso de fabricación, por tanto, estos límites impondrán restricciones adicionales al diseño. Este es un aspecto sobre el cual no se han encontrado referencias en la revisión bibliográfica realizada.

En este artículo se presenta un análisis de las restricciones impuestas por los límites tecnológicos de los elementos pasivos en el diseño de un LNA CMOS, de configuración fuente común con degeneración inductiva.

Primeramente se obtienen, a partir del análisis del circuito, dependencias cualitativas entre los valores de los elementos pasivos y los objetivos de síntesis del LNA (ganancia, corriente de polarización y ancho de los transistores), que permiten prever cómo los parámetros constructivos limitan el desempeño funcional del amplificador.

Estas dependencias fueron posteriormente comprobadas y enriquecidas a través de simulaciones, realizadas para una tecnología CMOS de 130 nm con 1.2 V de alimentación y una frecuencia de trabajo de 2.45 GHz. Para la topología estudiada, se muestra cómo la ganancia máxima, la corriente de polarización mínima (y, por tanto, el consumo de potencia mínimo) y las dimensiones de los transistores utilizados en el diseño pueden estar determinadas por los valores extremos de inductancia y capacidad disponibles en el proceso tecnológico.

Análisis teórico de los límites impuestos por los elementos pasivos en la síntesis del LNA Descripción y análisis del LNA de fuente común con degeneración inductiva

La Fig. 1 muestra el esquema básico de un CS-LNA con degeneración inductiva. La degeneración inductiva (a través de Ls) produce una componente resistiva en la impedancia de entrada sin introducir una fuente de ruido extra 19. El capacitor CX permite minimizar la figura de ruido para valores específicos de ganancia y consumo 13. El inductor de compuerta, Lg, se incluye para sintonizar la impedancia de entrada. El transistor M2 se utiliza como etapa cascode, para disminuir el efecto Miller sobre el transistor M1 y mejorar el aislamiento inverso 9. El inductor LD forma una red resonante paralela con las capacidades de salida de la etapa cascode y de la impedancia vista hacia la carga. El divisor capacitivo (C1, CP) se incluye para acoplar la impedancia de salida a los 50 Ω del analizador de espectro, que se utilizará en la caracterización experimental del LNA como circuito independiente. El resistor de polarización de compuerta (RG) y el capacitor de bloqueo de la componente de directa en la entrada (Cb) deben presentar impedancias suficientemente alta y baja, respectivamente, para que sus efectos sean despreciables bajo las condiciones normales de operación. Por su parte, la tensión de polarización de compuerta de M1 (VBIAS) puede ser obtenido a partir de VDD mediante un espejo de corriente o algún otro circuito que proporcione una referencia de tensión 20.

La ganancia de potencia disponible del LNA (G) puede expresarse mediante (1) en función de la transconductancia de la etapa de entrada (Gm=|Io/Vs| ), la resistencia de fuente (RS) y la conductancia de la etapa de salida [Go'=Re(Yo')]. Para obtener esta expresión se ha considerado que existe acoplamiento de impedancias en ambos puertos y se han despreciado las pérdidas en los capacitores de la red de acoplamiento de salida. En (1), VS e Io son valores efectivos.

La conductancia de la etapa de salida es el paralelo de la conductancia de salida de la etapa cascode [Re(Yod)] y la resistencia parásita paralela del inductor de drenaje (RD=ω0L DQD), siendo ω0 la frecuencia de trabajo y QD el factor de calidad de LD:

Mediante el análisis de pequeña señal con modelos simplificados (considerando en M1 solo la capacidad compuerta-fuente, Cgs, y el efecto transistor, io=gmvgs , tomando LS, Lg y CX como ideales y despreciando el efecto de carga de la etapa cascode sobre la etapa de entrada), la transconductancia con acoplamiento de impedancias en la entrada puede expresarse como 9:

Puede observarse en las expresiones anteriores que la ganancia del LNA depende tanto de las características del inductor de drenaje (LD) como de las del inductor de degeneración (LS); en el primero dependiendo del producto de su inductancia y su factor de calidad, mientras que en el segundo solo de su inductancia.

Por otra parte, en la selección del inductor de drenaje también es necesario tener en cuenta la respuesta en frecuencia de la impedancia de salida. Si se desea ampliar el intervalo de frecuencias para el cual la impedancia de salida tenga un valor adecuado se debe disminuir el factor de calidad de la red resonante, por lo que se debe escoger un valor bajo de QD. Para mantener el mismo aporte de la red de salida a la ganancia, cuando se disminuye QD debe aumentarse LD en la misma proporción. Sin embargo, el valor máximo de la inductancia está restringido tanto por los límites tecnológicos específicos de los inductores (que incluye la dependencia entre los posibles valores del factor de calidad con el valor de la inductancia 21) como por la capacidad mínima en la red resonante de salida 10. Debido a los compromisos y restricciones presentes en la selección del inductor de drenaje se propone que sean fijadas primero las características del mismo para luego seleccionar el resto de los elementos pasivos.

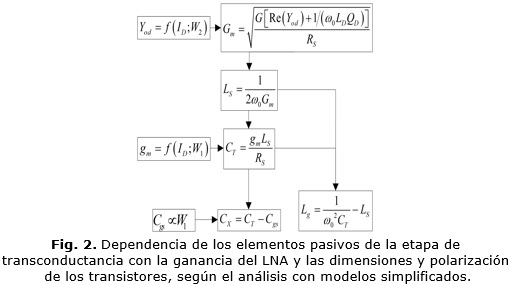

Del análisis de pequeña señal simplificado se obtiene un grupo de ecuaciones que permite establecer un orden lógico para determinar los elementos pasivos de la etapa de entrada. Este orden se muestra en forma de diagrama de flujo en la Fig. 2, incluyendo las dependencias con las dimensiones y polarización de los transistores 20, donde CT =CX+Cgs es la capacidad equivalente total entre la compuerta y la fuente de M1.

A causa de las simplificaciones realizadas en los modelos, estas expresiones no proveen la exactitud adecuada para calcular los valores de los elementos pasivos que serán utilizados en el diseño final, sin embargo, pueden utilizarse para prever las restricciones impuestas por los límites tecnológicos. A continuación se analizará cómo las variaciones de cada uno de los objetivos de síntesis del LNA (ganancia, corriente de polarización y ancho de los transistores) inciden sobre los valores de los elementos pasivos requeridos para garantizar la ganancia y el acoplamiento de impedancias.

Comportamiento de los elementos pasivos en función de los objetivos de síntesis Aumento del aporte de la etapa de transconductancia a la ganancia, manteniendo constantes la corriente de polarización y el ancho de los transistores

El aporte fundamental a la ganancia del LNA debe garantizarlo la etapa de entrada, mediante un valor suficientemente alto de Gm, para reducir la figura de ruido 9, 10. Según las expresiones mostradas en la Fig. 2, para aumentar Gm hay que disminuir el valor de LS, lo que a su vez implica una reducción de CT para mantener fija la resistencia de entrada (teniendo en cuenta que la transconductancia del transistor, gm, no varía para W1 e ID constantes). Tanto la disminución de LS como la de CT requieren un aumento de Lg para no alterar la frecuencia de resonancia. A su vez, para dimensiones fijas de M1 (Cgs constante) la disminución de CT es obtenida utilizando un menor valor de CX. Por tanto, el valor máximo de Gm puede estar limitado por los valores mínimos de LS (LSmín), de CX (CXmín) o el valor máximo de Lg (Lgmáx).

Disminución de la corriente de polarización, manteniendo constantes la ganancia y el ancho de los transistores

Para disminuir el consumo de potencia del circuito, con una tensión de alimentación constante, es necesario reducir el valor de la corriente ID. La variación de ID afecta la conductancia de salida de M2 20, sin embargo, si dicha conductancia es despreciable frente a la del inductor de drenaje, la conductancia de salida del LNA permanece invariable (2). Bajo estas condiciones, el valor de Gm también debe permanecer constante si se desea mantener fija la ganancia.

Suponiendo Gm constante, según las expresiones aproximadas de la Fig. 2 el valor de LS también debe permanecer invariable. Sin embargo, al disminuir la corriente de polarización disminuye la transconductancia de M1 (gm), lo que requiere una reducción del valor de CT para mantener fija la resistencia de entrada. Al igual que en el caso anterior, esto implica el aumento de Lg y la disminución de CX. Por tanto, el valor mínimo de ID puede estar limitado por los valores mínimo de CX (CXmín) o máximo de Lg (Lgmáx).

Límites en el ancho de los transistores, manteniendo constantes la ganancia y la corriente de polarización

En la metodología de diseño seguida para el LNA debe realizarse un barrido del ancho de los transistores para valores fijos de ganancia y corriente de polarización. Para analizar los efectos de las variaciones del ancho de los transistores se ha supuesto nuevamente Gm constante (por tanto, LS constante). Al disminuir el ancho de M1 (W1), con corriente constante, disminuye su transconductancia (gm) 20, lo que requiere la reducción del valor de CT. Esto último, como ya fue analizado, provoca el aumento de Lg. Por tanto, el valor mínimo de W1 puede estar limitado por Lgmáx. De forma contraria, el aumento del ancho de los transistores implicaría la disminución de Lg, aunque este efecto no debe representar una limitación práctica ya que implicaría el uso de transistores muy anchos, que no son habituales en aplicaciones de bajo consumo.

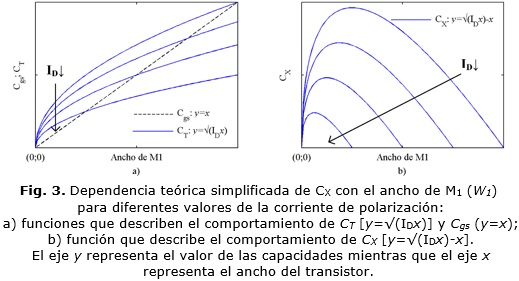

El análisis de la dependencia de CX con el ancho de los transistores es un poco más complejo. Cuando aumenta el ancho de M1 no solo aumenta CT, relacionado con gm, sino que también aumenta la capacidad intrínseca de M1, Cgs. Por tanto, el comportamiento de CX dependerá de la razón de cambio de CT y Cgs respecto al ancho del transistor: si CT aumenta más que Cgs para un mismo incremento de W1 entonces CX aumenta, y viceversa. La expresión (4) presenta esta doble dependencia, considerando como aproximación que la transconductancia es proporcional a la raíz cuadrada del producto corriente-ancho [√(IDW1)] y que la capacidad compuerta-fuente es proporcional al ancho del transistor 20. Tomando, como caso hipotético, que ambas constantes de proporcionalidad tengan valor unitario, en la Fig. 3 se ha graficado la dependencia de CX con el ancho del transistor para diferentes valores de la corriente de polarización.

En la Fig. 3b se observa que el valor máximo del ancho del transistor va a estar limitado por el valor mínimo de CX. Además, mientras menor sea la corriente de polarización menor será el valor máximo W1, por lo que la disminución del consumo de potencia limita las dimensiones de los transistores que puedan ser utilizadas en la implementación del LNA. Del comportamiento esbozado en la Fig. 4b también puede inferirse la existencia un intervalo de W1, en el entorno del máximo de la función, donde el valor de C X requerido sea mayor que el valor máximo de capacidad disponible en la tecnología. Sin embargo, como esto ocurre para los mayores valores de ID, este fenómeno no debe representar una limitante práctica al diseñar para valores bajos de consumo. Por tanto, el valor máximo de W1 puede estar limitado por CXmín.

Efectos secundarios no considerados en los modelos simplificados

Se ha demostrado en estudios previos sobre esta tecnología, que los efectos capacitivos del transistor M1 no considerados hasta el momento (la capacidad compuerta-sustrato, Cgb, y la capacidad compuerta-drenaje, Cgd) provocan una reducción de la ganancia de potencia respecto a la estimada en el análisis con modelos simplificados 10. Igualmente, la disminución de la corriente ID provoca un aumento de la impedancia de entrada de la etapa cascode (que es el inverso de la transconductancia de M2, gm2 20), lo que también produce la disminución de la ganancia.

Por tanto, mientras más anchos sean los transistores (mayores capacidades parásitas) o menor sea la corriente, se requiere un mayor valor de Gm para contrarrestar la disminución de ganancia introducida por ambas condiciones.

Esto implica que la corriente mínima y el ancho máximo de los transistores estarán limitados, además, por las mismas causas que limitan el máximo de Gm, o sea, LSmín, CXmín o Lgmáx (aunque, en el caso particular de Lg, el aumento de su valor como efecto secundario del aumento del ancho del transistor debe contrarrestarse con la disminución de esta inductancia prevista por el análisis con modelos simplificados para esta misma condición).

En la Tabla 1 se resume la influencia de los límites tecnológicos de los elementos pasivos sobre el diseño del LNA, según el análisis teórico realizado en esta sección. Se han incluido las consecuencias previstas a partir del análisis con modelos simplificados (efectos primarios) y las consideraciones realizadas sobre los efectos secundarios.

Verificación mediante simulaciones para una tecnología específica y aplicación en el diseño

Para comprobar y complementar los análisis realizados en la sección anterior se ha realizado una exploración del espacio de diseño utilizando los modelos proporcionados por el fabricante de la tecnología disponible: CMOS de 130 nm de longitud nominal del canal de los transistores, con una capa de polisilicio y ocho capas de metal (1P8M), con 1.2 V de alimentación. En la síntesis de los LNA se tomaron como especificaciones una ganancia mínima de 10 dB y acoplamientos de impedancia en ambos puertos por debajo de -10 dB, referidos a una impedancia de 50 Ω, en la banda de 2.4 a 2.5 GHz. Estos valores son requeridos para la implementación de un receptor ZigBee/IEEE 802.15.4 22, 23. Además, el ancho de M2 (W2) se estableció a W2=W1/2, para disminuir el aporte de este transistor a la capacidad de carga y así aumentar el margen de selección de la red de acoplamiento de salida 10. Se tomó la misma longitud de canal para todos los transistores (L1=L2=L), analizándose dos valores distintos: el mínimo permitido por la tecnología (Lmín = 120 nm) y el doble del mismo (2Lmín = 240 nm)

Características de los elementos pasivos disponibles

Los capacitores de la tecnología utilizada son del tipo metal-aislante-metal (MiM, por sus siglas en inglés), mientras que los inductores están formados por espiras octogonales y tienen la posibilidad de incluirles un plano de tierra para disminuir el acoplamiento con el sustrato 24 (Fig. 4).

Mediante simulaciones se obtuvieron los parámetros para el modelado del circuito de estos elementos a partir de sus características constructivas: para los capacitores el área de las placas paralelas (la separación entre las placas está fijada por la tecnología); para los inductores el número de vueltas, nt, el diámetro exterior, od, y el ancho de las espiras, w (la separación entre espiras, s, está fijada por la tecnología).

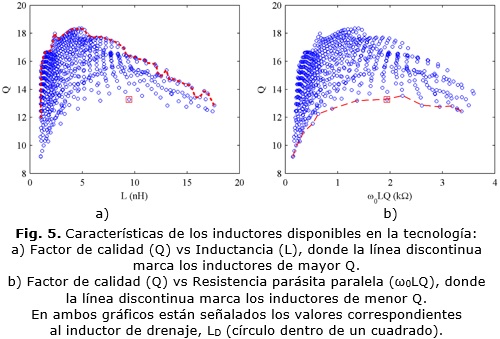

En el caso de los capacitores es posible obtener capacidades de hasta 5 pF con pérdidas despreciables respecto a la componente reactiva. Para los inductores, la relación entre las magnitudes de interés (inductancia, factor de calidad y resistencia parásita paralela) se encuentran graficadas en la Fig. 5.

De los posibles inductores, serán utilizados en compuerta y fuente (Lg y LS) los de mayor factor de calidad en cada intervalo de inductancia (Fig. 5a), para disminuir su aporte a la figura de ruido 9, 10, 21. El inductor de drenaje fue seleccionado entre los de menor factor de calidad en función de la resistencia parásita paralela (Fig. 5b), tomando valores intermedios de resistencia e inductancia (LD=9.5 nH; QD=13; RD≈2 kΩ).

A partir de estos valores es posible, de ser necesario, aumentar el aporte de este inductor a la ganancia con un ancho de banda aproximadamente constante (al aumentar la resistencia por encima de 2 kΩ el valor de Q presenta pocas variaciones), o bien aumentar el ancho de banda pero sacrificando el aporte a la ganancia.

Comportamiento de los elementos pasivos en función de los objetivos de síntesis en la tecnología disponible

El estudio del comportamiento de los elementos pasivos en función de los objetivos de síntesis fue realizado en dos fases. En la primera se realizó un barrido de la corriente de polarización (ID) y del ancho de canal del transistor M1 (W1), con una ganancia cercana al valor mínimo (10.5±0.5 dB). En la segunda etapa se fijó la corriente y se realizó un barrido de la ganancia y de W1.

Para cada combinación de ganancia, corriente y ancho de los transistores se buscaron, utilizando resultados de simulaciones, las dimensiones de los elementos pasivos que garantizan que el LNA correspondiente cumpla con los requerimientos de acoplamiento de impedancias (con un margen adicional de 5 dB) y el valor de ganancia deseado.

Variación de la corriente de polarización y del ancho de los transistores

En la Fig. 6 se muestran los valores de los elementos pasivos de los LNA sintetizados para una ganancia deseada de 10.5±0.5 dB, en función del ancho del transistor M1 y la corriente de polarización. Todos los LNA sintetizados presentan acoplamientos S11, S22<-15 dB y ganancias en el intervalo [10.3; 10.8] dB.

Con los resultados mostrados en la figura se comprueban los efectos primarios y secundarios previstos en los análisis teóricos. En la medida en que disminuye la corriente de polarización es necesario disminuir la inductancia de degeneración, aumenta el valor requerido de Lg y disminuye el de CX.

La inductancia LS se mantiene prácticamente constante respecto al ancho de los transistores para los mayores valores de ID. Sin embargo, mientras disminuye la corriente de polarización se hace más notable la disminución de LS con el aumento de W1. Este comportamiento es más crítico en los transistores de mayor longitud de canal.

Aparece además otro fenómeno, no previsto en los análisis realizados: la disminución de LS para valores pequeños de W1. La causa de este comportamiento puede estar asociada al aumento de las pérdidas en el inductor de compuerta (para valores pequeños de W1 el valor de Lg es mayor y su factor de calidad disminuye, como se observó en la Fig. 5a, lo que aumenta la resistencia parásita serie), que deben ser compensadas con un aumento de la transconductancia de la etapa de entrada. Esto implica, a su vez, un aumento de Lg y una disminución de CX adicionales a los previstos en el análisis. Puede comprobarse también el aumento del valor de Lg para valores pequeños de W1, mientras que para ID = 0.3 mA aparece el aumento de Lg con el incremento de W1.

En el caso de CX se comprueba el comportamiento previsto respecto al ancho de los transistores, dependiente además de ID, previsto en la Fig. 3. Cuando se aumenta W1 ocurre un incremento inicial de CX, hasta un valor máximo a partir del cual comienza a disminuir. Tanto el valor máximo de CX como el valor de W1 para el cual este ocurre, disminuyen mientras menor es la corriente de polarización.

En cuanto al largo del canal utilizado, con transistores de 240 nm los valores de CX son menores que con transistores de 120 nm. Esto se debe a que la capacidad intrínseca entre compuerta y fuente (Cgs) de M1 en el primer caso es mayor que en el segundo, por tanto, es necesario un menor valor de CX para mantener constante la capacidad equivalente total (CT) y no afectar la resistencia de entrada. Además, el valor de LS presenta una mayor variación en los transistores de 240 nm con la disminución de la corriente.

En el intervalo de dimensiones analizadas (16 a 104 µm para L = 120 nm y 32 a 208 µm para L = 240 nm) se demuestra cómo los límites tecnológicos restringen la síntesis del LNA. Para ambos tipos de transistores, con una corriente ID = 0.3 mA se requieren valores de Lg cercanos al máximo disponible en la tecnología (18 nH), por lo que no es posible sintetizar amplificadores con menor consumo de potencia. Se aprecia además cómo el valor máximo de Lg limita el ancho mínimo de los transistores para los menores valores de corriente de polarización.

Por otra parte, con los transistores de 240 nm, se puede observar también el acercamiento al límite mínimo de LS (1 nH) y CX (0 pF, o sea, ausencia de este capacitor) con el aumento del ancho para los menores valores de corriente, reduciendo el número de amplificadores sintetizables.

Variación de la ganancia del LNA y del ancho de los transistores

Para comprobar la dependencia entre los elementos pasivos del LNA con la ganancia se fijó la corriente de polarización a 0.4 mA y se sintetizaron amplificadores con distintos valores de ganancia, aumentando a partir de 10.5 dB. En la Fig. 7 se muestran los valores de los elementos pasivos para cada LNA sintetizado, en función del ancho del transistor M1 y la ganancia deseada. Todos los LNA sintetizados presentan acoplamientos S11, S22<-15 dB y ganancias con una diferencia modularmente menor que 0.3 dB respecto al valor nominal.

Con estos resultados se comprueban las dependencias establecidas mediante el análisis del circuito: el aumento de la ganancia requiere la disminución de LS y de CX, así como el aumento de Lg. Para ambos tipos de transistores la ganancia máxima queda determinada por el menor inductor realizable físicamente que puede ser utilizado como degeneración.

Con el aumento de la ganancia también disminuye el número de amplificadores que pueden ser sintetizados, debido a las limitaciones que impone el valor máximo de Lg sobre el ancho mínimo de los transistores, así como las impuestas por los valores mínimos de LS y de CX sobre el ancho máximo. Esta disminución es mayor si se incrementa el largo del canal de los transistores. El comportamiento de los elementos pasivos respecto a la variación del ancho de los transistores para cada valor de ganancia se corresponde con el análisis teórico y con los resultados obtenidos en el acápite anterior.

Exploración del espacio de diseño

La Fig. 8 muestra los resultados de las simulaciones a 2.45 GHz para la figura de ruido (NF) y el IP3 referido a la entrada (IIP3) de los LNA sintetizados con ganancia de 10.5±0.5 dB, para completar la exploración del espacio de diseño. En la figura están señalados los requerimientos para el receptor ZigBee 22, 23.

Todos los LNA sintetizados garantizan la especificación de la figura de ruido (NF<3 dB), pero la linealidad requerida (IIP3>-4 dBm) no se cumple para los valores más bajos de la corriente de polarización (ID=0.3 mA utilizando transistores de 120 nm e ID<0.5 mA con los de 240 nm).

Para ID=0.3 mA, con ninguno de los dos tipos de transistores puede asegurarse que se haya obtenido el pico del IIP3, ya que solo aparece la región decreciente de este parámetro respecto al aumento del ancho de los transistores. Esto ocurre porque no fueron sintetizados circuitos con transistores de menor ancho, debido a los límites impuestos por los elementos pasivos disponibles en la tecnología. En el caso de los LNA con transistores de 120 nm, en los picos del IIP3 para ID≥0.4 mA la linealidad obtenida supera notablemente el requerimiento establecido, por lo que pudiera esperarse un comportamiento similar para ID=0.3 mA si hubiera sido posible la síntesis de circuitos con W1<32 µm. Por tanto, los límites tecnológicos de los elementos pasivos inciden tanto de forma directa como indirecta en el consumo mínimo con el que puede diseñarse este tipo de amplificador.

CONCLUSIONES

En este trabajo se presentó un análisis de las restricciones impuestas por los límites tecnológicos de los elementos pasivos en el diseño de un LNA CMOS, de configuración fuente común con degeneración inductiva.

A partir de un estudio realizado de esta topología mediante el análisis del circuito y simulaciones, se obtuvo que la ganancia máxima, el consumo de potencia mínimo y las dimensiones de los transistores que pueden ser utilizados en el diseño, están determinadas por los valores extremos de inductancia y capacidad disponibles en el proceso tecnológico. De manera general, la disminución del largo del canal de los transistores aumenta el número de amplificadores que pueden ser sintetizados con los elementos pasivos de una tecnología específica. Los resultados obtenidos corroboran, además, la necesidad de incluir toda la información tecnológica posible de los elementos pasivos dentro del flujo de diseño de circuitos integrados para aplicaciones de radiofrecuencia.

AGRADECIMIENTOS

Este trabajo ha sido apoyado por CAPES-Brasil a través del Proyecto 176/12, CNPq, MAEC-AECID a través del proyecto FORTIN (Ref. D/024124/09), el programa FEDER de la Junta de Andalucía proyecto P09-TIC-5386, y el Ministerio de Economía y Competitividad proyecto TEC2011-28302 en España.

REFERENCIAS

1. Millman, J. y A. Grabel: Microelectrónica. 6 ed. Hispano Europea, S. A. Barcelona, España. 1993.

2. Baker, R.J.: CMOS. Circuit Design, Layout, and Simulation. 3 ed. John Wiley & Sons. Hoboken, NJ. 2010.

3. Sah, C.: «Evolution of the MOS transistor-from conception to VLSI»en Proceedings of the IEEE, Vol 76. No. 10, p. 1280-1326, 1988.

4. Woerlee, P.H., et al.: «RF-CMOS performance trends»en Electron Devices, IEEE Transactions on, Vol 48. No. 8, p. 1776-1782, 2001.

5. Vidojkovic, V., et al.: Adaptive Multi-Standard RF Front-Ends. Springer. 2008.

6. Schneider, M.C. y C. Galup-Montoro: CMOS Analog Design Using All-Region MOSFET Modeling. Cambridge University Press. New York. 2010.

7. Lee, T.H. y S.S. Wong: «CMOS RF integrated circuits at 5 GHz and beyond»en Proceedings of the IEEE, Vol 88. No. 10, p. 1560-1571, 2000.

8. Razavi, B.: RF microelectronics. Prentice Hall. Upper Saddle River, NJ. 1998.

9. Lee, T.H.: The design of CMOS Radio-Frequency Integrated Circuits. 2 ed. Cambridge University Press. Cambridge. 2004.

10. Leroux, P. y M. Steyaert: LNA-ESD Co-Design for Fully Integrated CMOS Wireless Receivers. The Kluwer International Series in Engineering and Computer Science. Springer. Dordrecht. 2005.

11. Farahani, S.: ZigBee Wireless Networks and Transceivers. Elsevier. 2008.

12. Shaeffer, D.K. y T.H. Lee: «A 1.5-V, 1.5-GHz CMOS low noise amplifier»en Solid-State Circuits, IEEE Journal of, Vol 32. No. 5, p. 745-759, 1997.

13. Andreani, P. y H. Sjoland: «Noise optimization of an inductively degenerated CMOS low noise amplifier»en Circuits and Systems II: Analog and Digital Signal Processing, IEEE Transactions on, Vol 48. No. 9, p. 835-841, 2001.

14. Belostotski, L. y J.W. Haslett: «Noise figure optimization of inductively degenerated CMOS LNAs with integrated gate inductors»en Circuits and Systems I: Regular Papers, IEEE Transactions on, Vol 53. No. 7, p. 1409-1422, 2006.

15. Aparin, V., G. Brown y L.E. Larson: «Linearization of CMOS LNA's via optimum gate biasing». en Circuits and Systems, 2004. ISCAS '04. Proceedings of the 2004 International Symposium on. 2004.

16. Niu, G., et al.: «Intermodulation linearity characteristics of CMOS transistors in a 0.13 µm process». en Radio Frequency integrated Circuits (RFIC) Symposium, 2005. Digest of Papers. 2005 IEEE. 2005.

17. Toole, B., C. Plett y M. Cloutier: «RF circuit implications of moderate inversion enhanced linear region in MOSFETs»en Circuits and Systems I: Regular Papers, IEEE Transactions on, Vol 51. No. 2, p. 319-328, 2004.

18. González Rios, J.L., et al.: «Reliability, power consumption and transistor sizing in 2.4 GHz CMOS LNAs». en Ninth International Caribbean Conference on Devices, Circuits and Systems. Playa del Carmen, Mexico. 2014.

19. Karanicolas, A.N.: «A 2.7-V 900-MHz CMOS LNA and mixer»en Solid-State Circuits, IEEE Journal of, Vol 31. No. 12, p. 1939-1944, 1996.

20. Razavi, B.: Design of Analog CMOS Integrated Circuits. McGraw-Hill. New York. 2001.

21. Fiorelli, R., F. Silveira y E. Peralias: «MOST Moderate-Weak-Inversion Region as the Optimum Design Zone for CMOS 2.4-GHz CS-LNAs»en Microwave Theory and Techniques, IEEE Transactions on, Vol 62. No. 3, p. 556-566, 2014.

22. Trung-Kien, N., et al.: «A Low-Power RF Direct-Conversion Receiver/Transmitter for 2.4-GHz-Band IEEE 802.15.4 Standard in 0.18-µm CMOS Technology»en Microwave Theory and Techniques, IEEE Transactions on, Vol 54. No. 12, p. 4062-4071, 2006.

23. Fiorelli, R., et al.: «2.4-GHz single-ended input low-power low-voltage active front-end for ZigBee applications in 90 nm CMOS». en Circuit Theory and Design (ECCTD), 2011 20th European Conference on. 2011.

24. Yue, C.P. y S.S. Wong: «On-chip spiral inductors with patterned ground shields for Si-based RF ICs»en Solid-State Circuits, IEEE Journal of, Vol 33. No. 5, p. 743-752, 1998.

Recibido:15 de enero de 2015

Aprobado: 19 de mayo de 2015

Jorge Luis González Rios, Centro de Investigaciones en Microelectrónica (CIME-CUJAE), La Habana, Cuba. E-mails: jorgeluis.gr@electrica.cujae.edu.cu, moreno@unifei.edu.br, dgarcia@imse-cnm.csic.es.